# **CLC522 Advanced Operating Considerations & Military Specifications**

January 1994

The CLC522 Variable Gain Amplifier is a versatile circuit that can be used in a wide variety of applications. The basic operation and specifications of the CLC522 are described in the datasheet for the CLC522; however, in many more demanding applications, the information contained in the datasheet is insufficient to analyze the expected performance. The purpose of this application note is to provide the additional information needed for analysis in some of these more demanding applications. The application note is a companion to the datasheet, and if you do not have a copy of the datasheet, one should be requested to obtain the full benefit from this application note.

#### **Frequency Response Determining Elements**

The CLC522 should be thought of as four separate amplifier elements in a single package. These are two very wideband, closed loop, unity gain buffers, a two quadrant multiplier core with gain control linearization, and a wideband current feedback op amp used as a transimpedance output stage. Both the buffer bandwidths and multiplier bandwidth are typically far in excess of the output op amp. It is therefore the frequency response of the output stage that typically sets the overall bandwidth for the CLC522. However, at high  $R_q$  values (low  $A_{vmax}$ ), the input buffers are peaking slightly. This allows R<sub>f</sub> to be increased to bandlimit the output amplifier as compensation for this input buffer peaking. Conversely, at very low  $R_{q}$ 's (high  $A_{vmax}$ ), the input buffers start to become the bandlimiting point. In this case, R<sub>f</sub> can be decreased from its nominal 1k value to peak the output amplifier. This partially compensates for the increased rolloff at the input due to heavy loading on the buffer outputs.

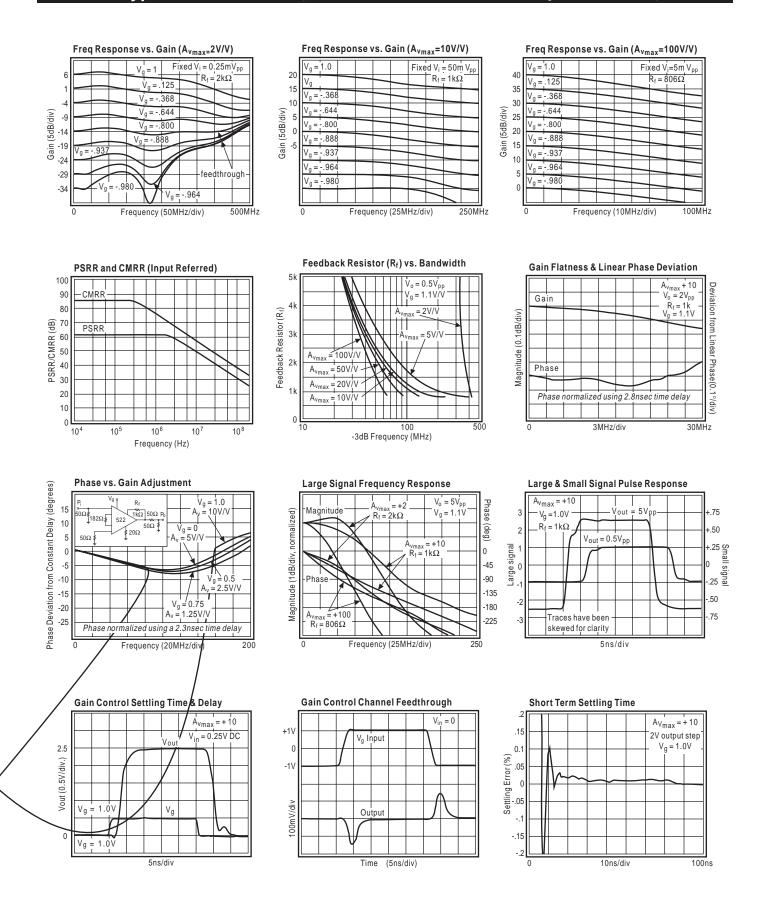

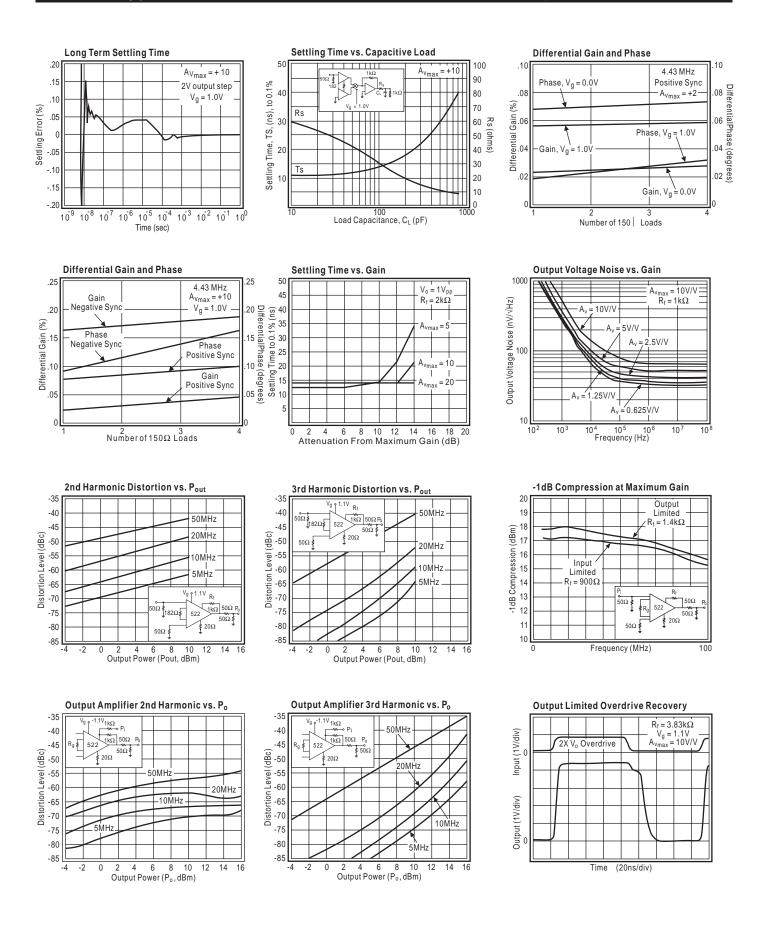

This discussion is reflected in plot 4 showing a suggested  $R_f$  vs.  $A_{vmax}$ . This plot shows the required  $R_f$  to most closely match the  $A_{vmax}$  = 10,  $R_f$  = 1k typical frequency response when operating with  $V_g$  = 1.1V. In addition, plot 6 shows the bandwidth reduction (at various  $A_{vmax}$  settings) for an increased  $R_f$  value. Increasing  $R_f$  will allow  $R_g$  to be increased, for a given desired  $A_{vmax}$ , which will allow a higher maximum differential (VA<sub>dmax</sub>) input signal to be applied.

Very little change in the frequency response is observed as  $V_g$  is reduced below +1 volt reducing the CLC522 signal gain from  $A_{vmax}$ . Since the frequency response is dominantly determined by the output amplifier, shunting signal away to ground in the 2 quadrant multiplier has little effect on the shape of either the magnitude or phase response (see plots 2, 3, 8, 9, and 10). When the CLC522

is actually being used as an attenuator, however, high frequency feedthrough will alter the shape of the frequency response at high frequencies (see plots 1 and 7).

# **Usable Gain Adjustment Range**

The gain of the CLC522 may always be varied from  $A_{vmax}$  to 0 as  $V_g$  is varied from +1 to -1. In applications where a maximum input voltage that is always less than Vdmax is to be applied, and the CLC522 is used to adjust the output swing, this full attenuation range is available. This application is reflected in plots 1 through 3. However, when the CLC522 gain adjust is used to compensate for a very wide range of input signals by increasing the gain at low inputs and decreasing the gain at higher inputs, there are very definite limits to the usable gain adjustment range. (This discussion of usable gain adjustment range will neglect the  $3\Omega$ 's added to  $R_g$  in setting the gain).

From a maximum gain set by  $A_{vmax} = 1.85 * R_f/R_q$ , the CLC522 can be thought of as an electrical attenuator as the gain control voltage is reduced below 1V. In situations where a constant maximum output signal voltage is desired, the maximum gain will be used at minimum input while the minimum gain will be used when the maximum input signal is present. This is not to say that the gain is being adjusted to hold a constant output voltage swing. Rather, the input signal is varying over a range of voltages and the CLC522 gain is being adjusted such that the maximum input signal is always being scaled to a desired maximum output voltage. Given the resistor values selected for R<sub>f</sub> and R<sub>q</sub>, along with the current limit on the input stage (I<sub>TAIL</sub>), a maximum attenuation from A<sub>vmax</sub> can be computed that satisfies the requirement that the maximum input voltage (at minimum gain) does not cause more than I<sub>TAIL</sub> to flow in R<sub>a</sub>.

It is useful here to discuss the gain range in terms of dB. It is also often useful to consider input and output sinusoidal voltage swings in terms of dBm. The gain from the differential input voltage to the output voltage in terms of dB is given by equation 1.

$$G_{dB} = 20 * log ((V_0+1) * A_{vmax}/2))$$

Eq. 1

Converting a sinusoidal voltage from a peak to peak swing into dBm can be done using equation 2.

$$P_{dBm} = 10 \log \left[ 20 \left( \frac{V_{pp}}{2\sqrt{2}} \right)^2 \right]$$

Eq. 2

Strictly speaking, this is the power in a  $50\Omega$  resistor referenced to 1mW. However, for the purposes of this discussion, a peak-to-peak voltage swing across any resistive load will be computed as in equation 2.

Given a maximum plus and minus current available in  $R_{\alpha}$ (±I<sub>TAII</sub>), this current, times 1.85, is the maximum (when  $V_{g} \ge 1.0$  volt) that is available to feed through  $R_{f}$  in producing a maximum available output pin voltage swing;  $V_{opp}(max) = 2 * 1.85 * I_{TAIL} * R_{f}$ . When the CLC522 gain is being adjusted to hold the output swing relatively constant, the desired maximum  $V_{\text{opp}}$  must be less than the V<sub>opp</sub>(max) shown above if there is to be any gain adjust range. As the gain is reduced from  $A_{\text{vmax}}$ , the available maximum current through R<sub>f</sub> is also being attenuated by the same amount that the gain has been attenuated. The gain can therefore only be reduced from A<sub>vmax</sub> until this attenuation in gain times 2 \* 1.85 \*  $I_{TAIL}$  \*  $R_f$  equals the desired maximum  $V_{opp}$ . The ratio of maximum available swing, V<sub>opp</sub>(max), to the desired maximum output voltage swing, V<sub>opp</sub>, is also the ratio of maximum gain to minimum gain. Equation 3 summarizes this discussion by showing the available gain range before input limiting occurs.

Linear (V/V) gain adjustment range

$$\frac{A_{Vmax}}{A_{vmin}} = 2*1.85*I_{TAIL}*\frac{R_f}{V_{opp}} = \beta$$

In log terms, gain adjust range =

$$20*\log\left(\frac{2*1.85*I_{TAIL}*R_{f}}{V_{opp}}\right)dB$$

Note that this gain adjustment range is independent of  $R_g$  and hence  $A_{vmax}$ . This will be the gain adjustment range available from any maximum gain selected for a given  $R_f$  and desired maximum  $V_{opp}$ .

The log form of equation 3 is used in plot 5 for  $I_{TAIL}$  = 1.8mA given a range of values for  $R_f$  swept over a wide range of desired maximum output voltage swings.

A CLC522 design may be done using these results. Given a required gain adjustment range, select an  $R_{\rm f}$  from plot 6 consistent with the desired bandwidth (with some assumption on  $A_{\rm vmax}$  at this point), then, entering plot 5 on the y-axis at the desired gain adjustment range go over to the intersection with the selected  $R_{\rm f}$  line and then extend downward to read off the available fixed output swing. If the available  $V_{\rm opp}$  is less than or equal to the desired level, using the minimum input voltage coming in, a maximum gain and hence  $R_{\rm g}$  may be resolved (Some iterating at this would be required since plot 6 is parametric in terms of  $A_{\rm vmax}$ ). If the required  $R_{\rm f}$  to get a desired bandwidth along with the gain adjust-

ment range requirement leads to a maximum  $V_{opp}$ , = (2 \* 1.85 \*  $I_{TAIL}/\beta$ ) that is less than desired, a fixed gain postamplifier should be used.

## **Gain Accuracy Considerations**

The CLC522 is intended to provide an exceptionally well controlled attenuation from  $A_{vmax}$  where the full gain adjust range is for a ground referenced  $V_g$  from -1 to +1 volt.  $V_g$  is actually compared to an internal reference developed from the negative supply voltage. Equation 4 modifies **equation 2(?)** to include the effect of the minus supply.

$$A_V = (1 + V_0/(0.2 * (|V_{FF}|))) * A_{Vmax}/2 \text{ V/V}$$

Eq. 4

For  $V_{\text{EE}}$  = -5, equation 4 reduces to equation 2. The effect of DC variations in Vee is to expand or contract the full scale gain control range. AC variations in  $V_{\text{EE}}$  will modulate the output dependent upon the input signal present. The PSRR (plot 36) is therefore only for the positive supply voltage since variations in the minus supply will show up at the output dependent on the input signal present. It is critically important, therefore, to keep the minus supply stable and free of high frequency noise.

# **Controlling DC Offsets**

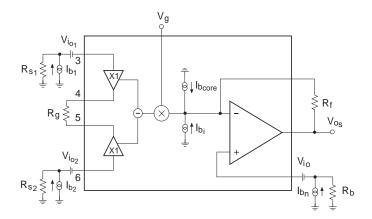

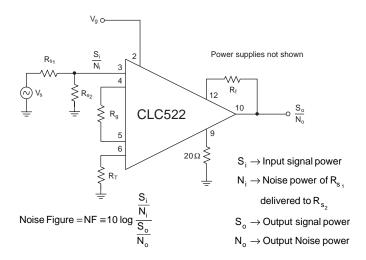

With no input signal present, there will always be a residual DC voltage at the output. This offset arises from input stage mismatches, a DC bias current at the 2-quadrant multiplier output, and output op amp DC error terms. Figure 1 shows the DC error model including all of these effects.

$$V_{os} = \pm \left(\frac{1}{2} \cdot 1.85 \frac{R_f}{R_g} (V_g + 1) \left(I_{b1} R_{s1} - V_{io1} - I_{b2} R_{s2} + V_{io2}\right) + \left(I_{bcore} + I_{b1}\right) R_f + I_{bn} R_b + V_{io2}\right)$$

Figure 1: DC Offset Model

The model of Figure 1 includes input bias currents and offset voltages for each of the two input buffers as well as the usual DC error terms for the output op amp. It also includes a  $V_g$  dependent current,  $I_{bcore}$ , that sums in parallel with the inverting input bias current of the output amplifier. This error current has a non-linear dependence

Eq. 3

on the gain adjust voltage, Vg. The buffer input bias currents are typically matched to closer than 0.1mA while the two buffer input offset voltages are matched to typically less than 1mV. To take advantage of this excellent bias current match at the buffer inputs (a low offset current), matched DC source impedances should be provided at the two buffer inputs.

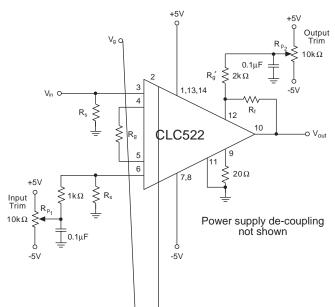

The output offset voltage may be improved using the adjustments shown in Figure 2.

Figure 2: Input and Output Stage DC Offset Adjustments

It will not be possible to completely null the output offset as the gain is adjusted since the Ibcore term in Figure 1 will vary non-linearly byer the gain adjustment range. However, a first order correction for the DC error terms of Figure 1 may be accomplished by removing any input signal (but retaining the DC source impedance) and making the following adjustments.

To correct for only the errors introduced by the output amplifier, the gain should be first adjusted to a minimum  $(V_q = -1)$ . With no contribution due to the input DC error terms,  $R_{p2}$  in Figure 2 may be used to sum a current into the inverting node of the output amplifier to cancel just the output amplifier DC error terms. This adjustment could alternatively be used to introduce a fixed (V<sub>a</sub> independent) offset into the output voltage. With the output amplifier's DC level determined by R<sub>p2</sub> while V<sub>p2</sub> < -1, returning V<sub>a</sub> to the maximum expected value (gain) will allow the input DC error terms to be cancelled. With Vg at the maximum value that will be used, R<sub>p1</sub> in Figure 2 may be adjusted to return the output voltage to the value measured when V<sub>q</sub> was at the minimum gain setting. This input adjustment is actually introducing an offset that is cancelling the effect of both the input buffer error terms and the effect of Ibcore at the maximum gain setting. The R<sub>p1</sub> adjustment of Figure 2 could alternatively be used to cancel a fixed DC component in the input signal. For this application, the input should be connected and Rp1 adjusted to move the AC component to the desired DC level at the output.

Adjusting the input and output stage offsets at the two gain extremes will hold the output DC error at a minimum at these two points in the gain range. The non-linear DC error introduced by the multiplier core will cause a residual, gain dependent, offset to appear at the output as the gain is swept from minimum to maximum. Also, neither the input nor the output offset adjustments described here will improve temperature drift effects.

Generally, a low R<sub>f</sub> will reduce the gain for the error current terms at the inverting input of the output amplifier. Note that matching R<sub>b</sub> to R<sub>f</sub> (in Figure 1) for bias current cancellation in the output op amp will not work for current feedback amplifiers, and, in any case, Rb should always be  $20\Omega$ . Due to good matching, the actual errors introduced by the input buffers is relatively minimal particularly with low, matched, source impedances (R<sub>s1</sub> = R<sub>s2</sub>). Although not shown in Figure 1, each of the input

buffers introduce a very well matched drop of approximately 0.9V from their inputs to output voltage across  $R_g. \\$  This common mode voltage level shift to the  $R_g$  resistor is of no consequence in normal operation, but should be kept in mind if DC paths are connected for some reason to pins 4 and 5.

#### **Noise Model**

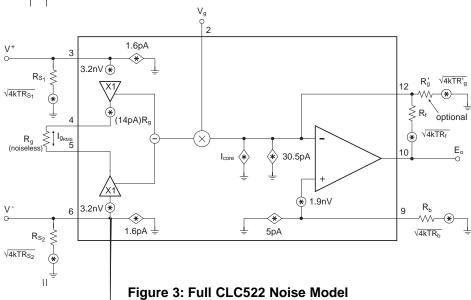

The complete noise model for a part as flexible as the CLC522 is necessarily somewhat complex. That model, with all of the external resistor noise sources included, is shown in Figure 3.

An optional resistor coming into the inverting pin of the output amplifier  $(R_g^{'})$  has been included in this model for completeness. This would be the impedance looking back towards either a DC offset adjust network or a separate signal source. Each of the noise voltages and currents in Figure 3 are spot noises (per  $\sqrt{\text{Hz}}$ ). To arrive at an expression for the total output spot noise (in  $nV/\sqrt{\text{Hz}}$ ) each of the noise sources of Figure 3 must be taken to the output by its gain and then squared. The total equivalent output noise is then the square root of the sum of squared contributing elements. See application note OA-12 for a general discussion of computing amplifier noise.

The analysis in equation 5 steps through developing the total output noise voltage from the model of Figure 3. This analysis generates an expression for the total output noise by first developing noise voltages squared (powers) for the output amplifier noise, then the contribution due to the input stage noise terms, and finally a gain and signal level dependent current noise term at the inverting input of the output amplifier, lcore, is considered.

Total output spot noise power  $\left(\frac{E_o^2}{1Hz}\right)$

$$\begin{split} E_o^2 = & \left[ \left( 1.9 nV \right)^2 + \left( 5 pAR_b \right)^2 + 4 kTR_b \right] \left[ 1 + \frac{R_f}{R_g^{'}} \right]^2 \\ & + 4 kTR_f \left( 1 + \frac{R_f}{R_g^{'}} \right) + \ldots \end{split}$$

Output amplifier noise terms

$$... + \left[ \left( 14pAR_g \right)^2 + 2\left( 3.2nV \right)^2 + \left( 1.6pAR_{s_1} \right)^2 + \left( 1.6pAR_{s_2} \right)^2 + 4kT \left( R_{s_1} + R_{s_2} \right) \right] \left[ \frac{1}{2} \left( V_g + 1 \right) 1.85 \frac{R_f}{R_g} \right]^2 + ...$$

Input stage noise terms

...+

$$\left(30.5pA + \left(12.4pA + 7.5pA\left(\frac{I_{g(RMS)}}{1mA}\right)\right)\left(1 - V_{g}^{2}\right)^{1.2}\right)^{2}R_{f}^{2}$$

Fixed term + Core current noise

$I_{g(RMS)}$  is the RMS current in  $R_g$  (include DC) in mA

Generally, most of these terms are negligible; with R $_{S_1}$ , R $_{S_2}$ , & R $_b$  relatively low and R $_g^{'}$  =  $\infty$

and  $\sqrt{4kTR_f}$  low relative to (30.5pAR<sub>f</sub>)

$$E_{o}^{2} \approx \left(\left(14pAR_{g}\right)^{2} + 2\left(3.2nV\right)^{2}\right)\left(\frac{1}{2}\left(V_{g} + 1\right)1.85\frac{R_{f}}{R_{g}}\right)^{2} + \left[\underbrace{30.5pA + \left(12.4pA + 7.5pA\left(\frac{I_{g(RMS)}}{1mA}\right)\right)\left(1 - V_{g}^{2}\right)^{1.2}}_{I_{confe}}\right]^{2}R_{f}^{2}$$

The I core noise term merits additional description. This term is actually modeling the noise injected through the gain adjustment input, V At either gain extreme, (for Va =  $\pm 1$ V), this term is zero. The I<sub>core</sub> noise current reaches a maximum for  $V_g = 0$  which would be at 1/2 of the maximum gain setting. At this  $V_{g}$ ,  $I_{core}$  shows a peak value that is dependent on the RMS current in the R<sub>q</sub> resistor. Noise in the V<sub>a</sub> path will modulate the gain for this input signal current. At maximum gain, all signal current is being passed on to the transimpedance stage and the Icore contribution is zero. Similarly, with the gain adjust channel shut off for  $V_g < -1V$ , no signal current is passed through the multiplier core and Icore is again zero. The maximum noise contribution through the V<sub>q</sub> channel is where exactly half of the signal current is being diverted to ground, at  $V_q = 0$ . The effect of this increasing  $I_{core}$  with reducing gain is to hold up the output noise through the first 6dB of attenuation from maximum gain. This is, for recommended R<sub>f</sub> values, only perceptible for a relatively low  $A_{vmax}$  as can be observed in plot 23 for  $A_{vmax} = 2$  and  $A_{vmax} = 5$ .

# **Computing Signal to Noise Ratio**

In applications where it is desired to hold a fixed output voltage swing ( $V_{opp}$ ), it is most meaningful to consider SNR at the output. In this application, the worst case SNR will generally occur at maximum gain,  $A_{vmax}$ . It is possible, at lower  $A_{vmax}$  settings, to see a slight degradation in SNR for the first 6dB of attenuation from maximum gain due to the effect of  $I_{core}$  as discussed in the previous section. However, the improved accuracy does not justify the complexity introduced by including this term in the SNR analysis. Therefore, a good approximation is that the worst case output SNR will

Eq. 5

occur at  $A_{vmax}$ . This would be when the input is at its minimum in applications that are using the CLC522 to move a very widely varying input range to more limited output range. While SNR will improve as the gain is reduced, harmonic distortion will be getting worse as the input signal range is increasing. Most distortion terms are set by the RMS current in  $R_g$  which will be at a maximum when the gain is at a minimum.

Using some of the operating constraints imposed on the CLC522, it is possible to significantly simplify equation 5 into a relatively simple expression for the worst case output SNR at  $A_{vmax}$ .

Continuing the assumptions of equation 5, (that  $R_{s1}$ ,  $R_{s2}$ , and  $R_b$  are low, that  $R_g^{'}$  is not present, and that the voltage noise of the output amplifier and the contribution of the  $R_f$  resistor noise is negligible), and evaluating this expression at  $A_{vmax}$ , yields the maximum output spot noise voltage.

$$E_{omax} = \sqrt{\left[\left(14pAR_g\right)^2 + 2\left(3.2nV\right)^2\right] \left(1.85 \frac{R_f}{R_g}\right)^2 + \left(30.5pA_f\right)^2} \text{ Eq. 6}$$

In situations where the minimum input voltage (V<sub>imin</sub>), maximum input voltage (V<sub>imax</sub>), and desired output voltage (Vopp) are known, both Rf and Rq will be determined by the gain and maximum differential input voltage constraints (see the discussion of usable gain adjust range). The expression for E<sub>omax</sub> can then be simplified using these constraints on R<sub>f</sub> and R<sub>a</sub>. One assumption that this analysis will make is that resistor values will be set up such that  $\pm I_{TAIL}$  will flow in  $R_g$  when the input is at its maximum peak-to-peak swing. This will make full use of the dynamic range of the CLC522. The discussion of input and output voltage swings are in peak -to-peak, but the current in  $R_{\rm g}$  is limited in a peak sense. One half of the peak to peak input voltage is therefore used in computing the peak current in R<sub>g</sub>. From equation 3 an expression for R<sub>f</sub> may be found by solving for either  $R_f$  or the gain adjust range,  $\beta$ .

$$R_f = \frac{\beta * V_{opp}}{\left(2*1.85*I_{TAIL}\right)} \text{ where } \beta = \text{linear gain adjust range}$$

$$\beta = \frac{V_{imax}}{V_{lmin}}$$

If it is also assumed that at minimum input we will operate at maximum gain (and neglecting for simplicity the  $3\Omega$  that is added to  $R_{\alpha}$  in setting  $A_{vmax}$ )

$$A_{vmax} = \frac{1.85 * R_f}{R_g} = \frac{A_{opp}}{V_{imin}}$$

The input stage current limit will constrain  $R_g$  as follows:

$$\frac{V_{imax}}{\left(2*R_g\right)} = I_{TAIL} (recalling that V_{imax} is peak-to-peak)$$

Solving for  $R_q$  and substituting for  $V_{imax} = \beta * V_{imin}$

$$R_g = \frac{\beta * V_{imin}}{\left(2 * I_{TAIL}\right)}$$

These three expressions constraining  $R_{\rm f}$ ,  $A_{vmax}$ , and  $R_{\rm g}$  may now be substituted into equation 6 to yield

$$\mathsf{E}_{omax} = \sqrt{\left[ \left( 14pA \, \frac{\beta V_{opp}}{2 I_{TAIL}} \right)^2 + 2 \left( 3.2 nV \right)^2 \right] \left( \frac{V_{opp}}{V_{Imin}} \right)^2 + \left( 30.5 pA \, \frac{\beta V_{opp}}{2*1.85*I_{TAIL}} \right)^2} \quad \text{Eq. 7}$$

After some algebraic manipulation equation 8 results

$$E_{omax} = \frac{\beta V_{opp}}{2 I_{TAIL}} \sqrt{(21.6 pA)^2 + 2 \left(3.2 nV \frac{2 I_{TAIL}}{V_{Imax}}\right)^2}$$

Eq. 8

Note that

$$\frac{V_{Imax}}{2I_{TAII}} = R_g$$

and that

$$\frac{\beta V_{opp}}{2I_{TAIL}} = 1.85 R_f$$

This greatly simplified expression for the maximum output spot noise may now be compared to the output signal voltage to get a worst case SNR. This will be done relative to the maximum  $V_{opp}$ . Recognize, however, that in any application the output voltage at any gain setting will be going below this  $V_{opp}$ . Dividing this maximum Vopp by the computed minimum SNR will tell how far below  $V_{opp}$  an signal may be discerned from the noise at the output. One way to do this is to convert the output spot noise to an integrated RMS noise voltage by multiplying equation 13 by the square root of the Noise Power Bandwidth -  $\sqrt{NPB}$  and dividing this into the RMS output voltage (( $V_{opp}/(2 * \sqrt{2})$  for sinusoids). Doing this yields:

Minimum SNR =

$$\frac{\frac{V_{opp}}{2\sqrt{2}}}{\frac{\beta V_{opp}}{2I_{TAIL}}\sqrt{\left(21.6pA\right)^2+2\left(3.2nV\frac{2I_{TAIL}}{V_{lmax}}\right)^2}\sqrt{NPB}}$$

Eq. 9

Simplifying equation 9 gives

Minimum SNR =

$$\frac{\frac{l_{TAIL}}{\beta}}{\sqrt{(21.6pA)^2 + 2\left(3.2nV\frac{2l_{TAIL}}{V_{Imax}}\right)^2}\sqrt{2NPB}}$$

Eq. 10

It is important to note that the value for V<sub>imax</sub> strongly influences the minimum SNR. As V<sub>imax</sub> becomes relatively small, the minimum SNR can become rapidly larger. Setting the two noise currents under the radical equal and solving for V<sub>imax</sub> will yield a crossover point where the effect of V<sub>imax</sub> starts to dominate. Using I<sub>TAIL</sub>= 1.35mA, this yields  $V_{imax} = 0.57 \text{Vpp}$ . For  $V_{imax} > 0.57 \text{V}_{pp}$ , this second term in the radical rapidly becomes negligible and the achievable minimum SNR reaches a floor set by the 21.6pA term. For  $V_{imax} < 0.57V_{pp}$ , the minimum SNR will decrease steadily with decreasing V<sub>imax</sub>. It is also important to note that the output SNR will improve from the value computed in equation 10 as the gain is reduced from A<sub>vmax</sub>. This follows from the assumption that the input signal is increasing as the gain is reduced below  $A_{vmax}$ .

# **Example Calculation of Minimum SNR**

Using the results of the previous section, it would be instructive to step through an entire design. As an example, use the following design information:

$$V_{imax}$$

= 1 $V_{pp}$

$\beta$  = 10 (gain adjustment range, implies  $V_{imin}$  = 0.1 $V_{pp}$ )

$I_{TAIL}$  = 1.35mA

NPB = 50MHz

Then, using equation 10 to get the worst case SNR (in RMS/RMS)

Minimum SNR =

$$\frac{\frac{1.35\text{mA}}{10}}{\sqrt{(21.6\text{pA})^2 + 2\left(3.2\text{nV}\frac{2(1.35\text{mA})}{1\text{V}_{pp}}\right)^2}}\sqrt{2*50\text{MHz}}$$

Eq. 11

This result states that when the input signal is ranging up to  $0.1V_{pp}$  (and the CLC522 is set at a maximum gain of whatever is needed to get to a desired  $V_{opp}$ ) the input signal can range down as low as  $0.1V_{pp}/544 = 0.18 mV$  and have an RMS power at the CLC522 output equal to RMS noise power. It is very interesting to note that although the actual value for the desired  $V_{opp}$  will have no impact on the minimum SNR, it will, along with the desired gain adjustment range and  $I_{TAIL}$ , determine the required value for  $R_f$ . Continuing this example to determine the  $R_f$  and  $R_g$  values, and targeting a  $V_{opp} = 1V_{pp}$  (which will set  $A_{vmax} = 10$  to get  $1V_{pp}$  at the output when  $V_{ipp} = 0.1V_{pp}$ ).

$$R_{f} = \frac{\beta * V_{opp}}{\left(2*1.85*I_{TAIL}\right)} = \frac{10*1V_{pp}}{\left(2*1.85*1.35mA\right)} = 2002\Omega$$

(from Eq. 3)

and

$$R_g = \frac{R_f * 1.85}{A_{vmax}} = \frac{2002 * 1.85}{10} = 370\Omega$$

(recall that the physical  $R_g$  resistor must be  $3\Omega$  lower to account for the buffer output impedances)

Checking whether the I<sub>TAIL</sub> current limit in R<sub>q</sub> is satisfied

$$I_{gmax} = (V_{imax}/2)/R_{g} = (1V_{pp}/2)/370 = 1.35mA$$

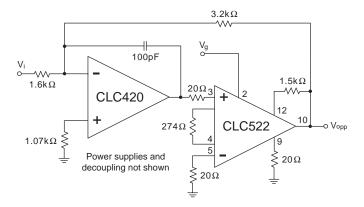

And finally, checking plot 6 for the CLC522 bandwidth that will result for an  $R_f$  = 2000 and  $A_{vmax}$  = 10 shows approximately 74MHz. Some means of setting the NPB to 50MHz after the CLC520 will be required to get the above results.

An alternative design approach would control  $R_f$  to get a desired bandwidth using an assumed  $A_{vmax}$  and plot 6. The only modification to the foregoing analysis is that, with  $R_f$  given along with the gain adjust range  $(\beta)$  and  $V_{imax},$  the minimum SNR expression is unchanged but the achievable output voltage is set by the expression used earlier for  $R_f.$

Solving R<sub>f</sub> =

$$\frac{\beta * V_{opp}}{(2*1.85*I_{TAIL})}$$

for  $V_{opp}$

$$V_{opp} = \frac{R_f * 2 * 1.85 * I_{TAIL}}{\beta}$$

Re-doing the previous example while targeting an R  $_{\rm f}$  = 1000  $\!\Omega$  yields the same SNR and R  $_{\rm g}$  value but V  $_{\rm opp}$  goes to

$$V_{opp} = \frac{1000 * 2 * 1.85 * 1.35 mA}{10}$$

and the maximum gain has dropped to  $\frac{1.85*1000}{370} = 5$

Going to plot 6 at  $R_f = 1k$  and  $A_{vmax} = 5$  shows a 220MHz bandwidth.

If it becomes necessary to set  $R_f$  to achieve a particular bandwidth, and to take whatever  $V_{opp}$  that results, a fixed gain post amplifier can be used to adjust the  $V_{opp}$  to a higher level if desired. It would be a very poor post amplifier that would degrade the SNR from that available at the output of the CLC522.

In summary, when the CLC522 is being used to scale a varying input range to a fixed output range, the minimum SNR at the output will occur at the maximum gain setting since this is the operating condition when the input is at a minimum. From equation 10, this minimum SNR depends only on the maximum current allowed in  $R_g$  (I\_TAIL), the desired gain adjust range ( $\beta$ ), the maximum anticipated input signal, the noise power bandwidth, and some constant noise terms associated with the CLC522. This minimum SNR is independent of the desired  $V_{opp}$ . The value for the feedback resistor ( $R_f$ ) will simultaneously set both  $V_{opp}$ ,  $A_{vmax}$ , and the CLC522 bandwidth. The primary design job is then to make the correct tradeoff's is getting to a value for  $R_f$ .

#### Using the Output Amplifier Separately

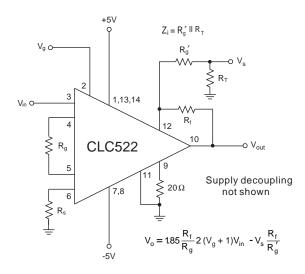

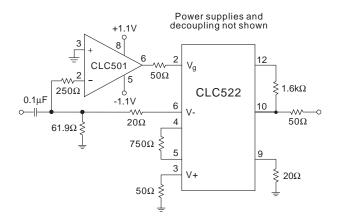

Although the output op amp is principally intended as a transimpedance stage for the signal current coming out of the gain adjustment stage, it can also be used as an inverting op amp for additional signals. The non-inverting input of this op amp is also available on pin 9. However, this pin should never be used to inject signal or offsets. Pin 9 should always be connected to a good ground plane through a  $20\Omega$  resistor. Figure 4 shows an example of how a high frequency signal may be summed into the output (with a gain of -1 in this case) independently of the output signal due to the gain adjusted input on pin 3.

Figure 4: Using the Output Amplifier to Sum in a Separate Signal

The circuit of Figure 4, with  $V_g < -1$  volt,  $R_t$  set to get  $R_g'|R_t = 50\Omega$ ,  $R_f = 1$ k, and a series output  $50\Omega$  resistor into a  $50\Omega$  load, was used to illustrate the output amplifier performance for plots 27, 30, 31, 32, and 33. These plots show that the output op amp is an exceptional amplifier in and of itself. The output op amp configured as an inverting amplifier offers a small signal bandwidth in excess of 200MHz (for inverting gains  $\le$ 2), 2nd & 3rd harmonic distortion powers greater than 60dBm less than the fundamental for output signals  $\le$ 20MHz and  $\le$ 2Vpp (10dBm) into a 100W load, and a 2-tone 3rd order intercept 3 35dBm for frequencies <20MHz (defined at a matched  $50\Omega$  load).

The output op amp should not be used for inverting gains >5. As this inverting gain is increased beyond this, 2nd order effects will start to limit the bandwidth for signal current from the gain adjust stage. In addition, higher inverting gains will begin to contribute significant errors from the output op amp's non-inverting input offset voltage and noise.

# **Predicting Harmonic Distortion (still in development)**

The total harmonic distortion present at the output will be a combination of both input stage and output amplifier effects. The output amplifier's harmonic distortion sets a minimum distortion level that can be expected (see plots 31 and 32). The output amplifier shows exceptional 2nd harmonic distortion but a 3rd harmonic term that increases rapidly with power and frequency. The input stage contributes a 2nd harmonic distortion that depends only on the power level in the  $R_g$  resistor and is relatively independent of the gain setting. In fact the input stage shows a very good match to a 2nd order intercept model. (Some statement here on 3rd harmonic distortion)

#### Limits to I/O Range and Overdrive Recovery

Several factors can limit the input and output voltage ranges. In most cases, the input stage will limit before the output stage has reached its maximum voltage swing. The maximum current available through R<sub>f</sub> is simply 1.85 \*  $I_{TAIL}$ . As long as 1.85 \*  $I_{TAIL}$  \*  $R_f$  <  $V_{omax}$ , the input stage will always limit due to ITAIL before the output amplifier can reach it's maximum ± voltage (i.e. V<sub>omax</sub>). For the output amplifier to be the limiting case,  $1.85 * I_{TAIL} * R_f <$  $V_{\text{omax}}$ . With  $I_{\text{TAIL}} = 1.8 \text{mA}$  and  $V_{\text{omax}} = 3.7 \text{ volts}$ ,  $R_{\text{f}}$  must be >1.1k $\Omega$ . Thus far, only the maximum gain case has been considered. This is when the full 1.85\*ITAIL is passed on through the multiplier core to the output transimpedance stage. As the gain is reduced from A<sub>vmax</sub>, and less maximum current is available to R<sub>f</sub>, the voltage swing limit will eventually return to the input stage even for high R<sub>f</sub> values. This can be shown by equating the available maximum current through R<sub>f</sub> to the output amplifier's voltage limit as shown in equation 12.

$$V_{omax} = 1.85 I_{TAIL} R_f \left( \frac{V_g + 1}{2} \right)$$

Eq. 12

Solving for the required  $V_g$  to have an equal input and output limit (note that this is a bipolar limit) -

$$V_g = \frac{V_{omax}}{1.85 I_{TAII} R_f} - 1$$

Eq. 13

As an example, consider a low  $A_{vmax}$  case with  $R_f = 2k\Omega$ ,  $I_{TAIL}$  = 1.8mA and  $V_{omax}$  = 3.7 Volts. At  $A_{vmax}$ , the voltage swing limit will be set by the output stage to V<sub>omax</sub> since  $R_f > 1.1k\Omega$ . Solving equation 13 for this example shows that for  $V_a$  < 0.11 Volt the voltage limit will move to the input stage. Once the swing limit has moved to the input, the right side of equation 12 is what is available at the output. Recall that this input limit is simply the differential input voltage that causes I<sub>TAIL</sub> to flow in R<sub>q</sub>. This discussion can provide another approach to computing the available attenuation from maximum gain for a fixed desired output voltage swing. Substituting a desired V<sub>opeak</sub> into equation 12 in place of V<sub>omax</sub>, (and recognizing that this peak swing is actually available as a peak-to-peak swing since ITAIL is bipolar), will yield the minimum  $V_g$  before input stage limiting occurs. If this expression for  $V_g$  is substituted into  $20 * log((V_g+1)/2)$  (which is the log form of attenuation vs.  $V_g$ ), equation 14 results -

available attentuation =

$$20 \log \left( \frac{V_{opeak}}{1.85 I_{TAIL} R_f} \right)$$

Eq.14

This is simply the earlier expression for gain adjust range, equation 3, with  $V_{opp}/2$  replaced by  $V_{opeak}$  and the fraction flipped over to give negative numbers for the maximum attenuation. Output limited overdrives recover much more quickly than input limited overdrives. This can be seen in the typical overdrive recovery waveforms of plots 37 and 38.

An important additional limit to operation is in the Vg input. Vg input voltages beyond the control input range of  $\pm 1 \text{V}$  run the risk of saturating internal nodes which will severely degrade the apparent gain control channel bandwidth as Vg is brought back into range. This gain control channel saturation can change the loop dynamics in a continuous feedback adjustable gain circuits. If this slowing down of the gain control response is problematic, a limit of -2V < Vg < +1.2V should be observed to avoid internal saturation on the gain adjust channel.

#### RF Specifications

Several dynamic range characteristics are unique to RF amplifier descriptions. The RF specifications that can be applied to the CLC522 include noise figure, 2-tone, 3rd order intercept, and -1dB compression. While the noise figure is an input referred specification, (with some assumption on source impedance), the intercept and compression specifications are commonly in reference to an output power at a matched  $50\Omega$  load. For these RF specifications, then, it will be assumed that a series  $50\Omega$ resistor to a  $50\Omega$  load is present at the output. The gain that has been previously discussed as a voltage or dB gain from the input pin to the output pin will now be to this matched load instead. Hence, the input to output gain will be cut in half or decreased by 6dB. Also, all of these specifications are assuming purely sinusoidal inputs. For further reference, application note OA-11 defines each of these specifications and describes how to apply them to op amp type amplifiers. In addition, a spreadsheet that will calculate the noise figure and 2-tone spurious levels over a wide range of operating conditions is available from the Comlinear applications department.

### **Noise Figure**

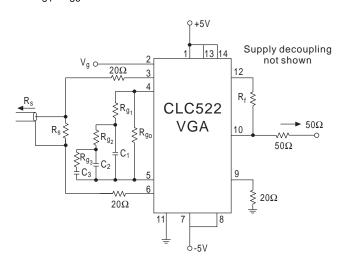

The noise figure for a device is a measure of the degradation in Signal-to-Noise ratio in going from the input to the output. The input noise is taken to be the noise power delivered by the source resistor to the input impedance of the amplifier circuit. Figure 5 shows this definition for the CLC522.

**Figure 5: Noise Figure Definition**

Every term in this noise figure equation is a power - which is considered in this case to be a voltage^2. After some manipulation, and setting  $R_{s1} = R_{s2} = R_s$ , the noise figure can be easily written in terms of the total noise voltage at the output pin and the voltage gain from the input to output pins as follows:

NF =

$$10 \log \frac{e_0^2}{A_v^2 R_s kT}$$

Eq. 15

where  $e_o \rightarrow total output noise voltage$

$A_v \rightarrow \text{voltage gain from pin3} \rightarrow \text{pin 10 in V/V}$

$$R_{s1} = R_{s2} = R_{s}$$

$$kT = 4E - 21(at 290^{\circ}k)$$

This expression for noise figure can then use equation 5 (or the more complete expression for output noise) to compute the noise figure for any particular gain and resistor values. The noise figure discussed here is for a 1Hz bandwidth (i.e. spot noise figure). Plot 24 shows this spot noise figure (for  $R_s = 50\Omega$  and each input terminated to ground in  $50\Omega s$ ) using equation 15 and the complete expression for total output noise.

### 2-tone, 3rd Order, Intermodulation Intercept

A simple model for an RF amplifier will typically project that 3rd order intermodulation spurious powers will increase 3dBm for every 1dBm increase in two signal powers at two closely spaced frequencies. If the average frequency of the two high power signals is taken to be  $F_{\rm o}$ , with an equal spacing of DF around this center frequency, the two 3rd order spurious terms will fall at  $F_{\rm o} \pm 3\Delta F$ . Assuming equal powers  $(P_{\rm o})$  in the two desired signals, equal 3rd order spurious powers  $(P_{\rm s})$  will also result. At any particular frequency,  $F_{\rm O}$ , equation 16 shows how an intercept (IM3) can be defined from a single measurement of Po and Ps (where  $P_{\rm o}$  and  $P_{\rm s}$  are powers in dBm at the matched load).

$$IM3 = P_0 + \frac{(P_0 - P_s)}{2} dBm$$

Eq. 16

The utility of this estimate of intercept is that given IM3 and equal two tone output signal power levels, the spurious power at the intermodulation frequencies may be predicted as shown in equation 17.

$$P_s = 3 * P_0 - 2 * IM3 dBm$$

Eq. 17

or, in terms of how far below the desired signals the spurious are,

$$P_0 - P_s = 2 * (IM3 - P_0) dBc$$

Eq. 18

National application notes OA-11 and OA-22 treat in considerable detail this intercept model for predicting 2-tone intermodulation distortion levels.

The 2-tone intermodulation spurious powers at the output of the CLC522 are a combination of 3rd order distortion mechanisms in both the input stage and the output amplifier. In most cases, the 3rd order distortion in the Rg current will dominate in setting the intermodulation distortion at the output. Since this is a case of cascaded amplifier intermodulation distortion, a single IM3 number for the total amplifier is not applicable. However, separate IM3 values for the input stage and the output amplifier will allow the calculation of the spurious power levels at the output.

Using the two intercepts in plot 27, a total output spurious level may be estimated. Since distortion is coming in at two points in the CLC522, (for a single pair of desired signal frequencies), the distortion introduced at the input will have a fixed (but unknown) phase relationship to the distortion introduced by the output stage. A reasonable estimate would be to assume that these two sources of distortion are in quadrature and will add together as the square root of summed squared voltages. Given a desired two tone power level at the matched load ( $P_{\rm o}$ ), and a gain from input to output, the two contributions to the spurious power at the output ( $P_{\rm s}$ ) will be -

$$P_{S_0} - 3P_0 = 2IM3_0 dBc$$

Eq. 19

Output amplifier term

$$P_{so}^{'} = 3P_o - 2\left(IM3_i + G_{dB} - 6 + 10\log\frac{R_g}{50}\right)dBm$$

Eq. 20

Input stage term taken to output

IM3 $_{\rm o}$  and IM3i are taken from plot 27 at the frequency of interest. Note that GdB is the log gain from the input to output pins (equation 1) and the 6dB term in the expression for P $_{\rm so}$  accounts for the 6dB loss in going from the output pin to the matched load. Since the input stage distortion really depends on the current in the R $_{\rm g}$  resistor, the input power must be converted to a power in R $_{\rm g}$ . This

is the effect of the  $10 * \log(R_g/50)$  in the expression for  $P_{s_0}$ . Given these two contributions to the 3rd order spurious power, equation 21 combines these into a typical combined spurious power.

$$P_{st} = 10 \log \left( 10^{\frac{P_{so}}{10}} + 10^{\frac{P'_{so}}{10}} \right)$$

Eq. 21

general, the input stage spurious  $(P_{so})$  will be the dominate contribution to the output 3rd order spurious power. The input generated spurious will be greater than the output stage spurious as long as the condition shown in equation 22 is satisfied.

The output stage will dominate only for high  $G_{dB}$ . The IM3 $_{o}$  of plot 27 is appropriate for  $R_{f}$  = 1k. This plot would also apply for additional signals brought into the inverting input of the output amplifier. The value of IM3 $_{o}$  for other values of  $R_{f}$  should be adjusted by subtracting 10 \* log ( $R_{f}$ /1k) from the value determined from plot 27 at the operating frequency of interest. This will approximately account for the change in loop gain in the output amplifier for different values of  $R_{f}$ .

This model for predicting the 3rd order spurious powers only holds for operation in the linear region of the CLC522. The principal limit in operating region is directed at not exceeding  $I_{TAIL}$  at the input for the peak value of the input 2-tone sinusoidal waveform. For equal powers  $(P_o)$  at the matched load, equation 23 computes the peak  $I_{R_0}$  through the gain setting resistor,  $R_g$ .

$$I_{R_{g(peak)}} = 2000 \sqrt{\frac{0.002}{R_g}} 10^{\left(\frac{P_o + 6 - G_{dB}}{10}\right)} \text{ mA} \qquad \text{Eq. 23}$$

Test data on the CLC522 indicates that this model for the output 2-tone spurious power holds well for  $I_{R_0(peak)}$  < 2.2mA.

As an example, consider calculating the 3rd order 2-tone spurious power levels for the following set of conditions -

$A_{vmax} = 20V/V$  (26dB) to output pin: 20dB to matched load

$R_f$  = 2.5k $\Omega$  to yield enough gain for  $I_{TAIL}$  to get  $4V_{pp}$   $R_g$  = 231 $\Omega$  to satisfy 1.85 \*  $R_f/R_g$  = 20 (physical  $R_g$  = 229) Atten = 6dB (V $_g$  = 0) operating gain to load = 5 (14dB)  $P_o$  = 4dBm (1V $_{pp}$  each tone, 2V $_{pp}$  for the 2-tone envelope)  $F_o$  = 20MHz (Test frequencies at 20MHz ±100kHz)

From this, various limits to operation should be checked.

Total output pin voltage swing  $-> \pm 2V$  into  $100\Omega$  Peak output current -> 2/100 = 20mA Peak slew rate at output  $-> 2V * (2*\pi*20$ MHz)= 251V/msec Peak current in R<sub>0</sub> -> (2/5)/231 = 1.73mA

All of these are within the operating range of the CLC522. The output 3rd order spurious may now be calculated using the expressions developed previously.

http://www.national.com

9

$$IM3_o = 40dBm - 10log(2500/1000) = 36dBm$$

(from plot 27 adjusted for R<sub>f</sub> = 2.5k)

IM3<sub>i</sub> = 16dBm (from plot 27 at 20MHz)

$$P_{s_0} = 3*4 - 2*36 = -60dBm$$

output amplifier term

(equation 19)

$$P_{S_0}' = 3 * 4 - 2 * (17 + 20 - 6 + 6.6) = -63.2dBm$$

input amplifier term (equation 20)

$$P_{st} = 10 * log(10^{(-60/10)} + 10^{(-63.2/10)})$$

= -58.3dBm

combination of input and output spurious contributions (equation 21)

In this case, the output amplifier is setting the 2-tone spurious level. The delta from the 4dBm single tone power level to the spurious power is 4 - (-58.3) = 62.3dBc. Note also that the 2.5k $\Omega$  feedback resistor will drop the bandwidth to 49MHz (from plot 6).

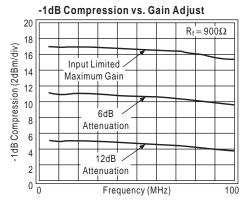

# -1dB Compression

This performance measure, like 2-tone intercept, is defined for the power at a matched  $50\Omega$  load. The plot of input and output -1dB compression (plot 30) is therefore for a power that is across a  $50\Omega$  resistor to ground with an additional  $50\Omega$  series resistor from the output pin of the CLC522 to this load resistor. The -1dB compression power is tested by sweeping the input power, at a fixed frequency, and observing where the output power is 1dBm less than what the low power gain would predict. This measurement is then repeated over a range of frequencies. The reported -1dB compression power is this actual measured power plus the 1dB it has been compressed.

Again, there is both an input and an output limit that can determine the -1dB compression. The output amplifier's voltage swing limit will set the -1dB compression point when the available signal current through the multiplier core times Rf will exceed the swing limit in the output amplifier. For an output limited case,  $R_f * I_{TAIL} * (V_o + 1)/2$ > Vomax. Hence, output limiting can occur principally for higher R<sub>f</sub>'s and at maximum gain settings. For the maximum gain case of plot 30, an output limited compression is obtained for  $R_f = 1.4k\Omega$  while an input limited operation is obtained for  $R_f = 900\Omega$ . When a swing limit has been reached at lower frequencies, either for an output voltage or input Rg current limit, the output waveform approaches a square wave for a sinusoidal input. At these low frequencies (<40MHz) and for any gain setting, the -1dB compression power at the matched 50W load will be the minimum of -

a. 16.8dBm (due to output amplifier voltage swing limits)

b.  $13.1 dBm + 20 * log(1.85 * I_{TAIL} * R_f * (V_g+1)/4)$  (input limited)

It is interesting to note that, once Vg has been reduced to cause the input limit to set the output -1dB compression, the output compression will decrease directly with signal gain. Figure 6 shows this clearly where the output -1dB compression over frequency shifts directly with gain setting when the input limit is setting the available output power.

Figure 6: -11dB Compression vs. Gain Adjust

Although the preceding discussion gives a good predictor of -1dB compression, this number does not provide a good predictor of 2-tone 3rd order intercept. The simplified assumption that the intercept is 10dBm above the -1db compression does not hold for the CLC522. The full model developed in the previous section should be used to predict 3rd order intermodulation spurious levels.

# Advanced Applications

Each of the following applications circuits exploit one or several unique feature in the CLC522. Please contact the Comlinear applications group for additional information on any of these applications.

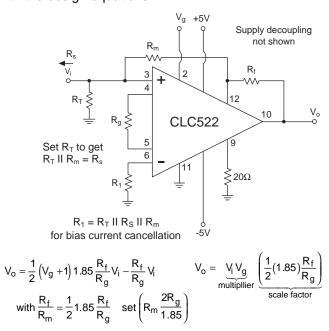

#### **Differential Amplifier**

The two buffers at the input of the CLC522 provide a high input impedance, matched frequency response path, for implementing a differential amplifier (see Figure 2). Any differential signal impressed across  $R_{\rm g}$  is transformed into a single ended current signal through  $R_{\rm g}.$  This provides an exceptional differential to single ended conversion right at the input stage. With the added flexibility of being an adjustable gain part, the CLC522 can be used to implement a very wideband differential amplifier. Application note OA-16 discusses this application for both the CLC522 and CLC520.

# **Differential Line Equalizing Receiver**

Extending the idea of a differential amplifier to a line receiver, and recognizing that the gain setting element can be used to shape the frequency response, an equalizing receiver can be easily implemented as shown in Figure 7.

The gain setting network shown in figure 12 implements a series of zero/pole pairs that can be placed to compensate the  $1/\sqrt{f}$  rolloff typically seen in long coax cables. At low frequencies, the gain starts out set by only  $R_{\rm go}$ .

or

The resistor & capacitor values are set such that C3, C2, and C1 short out sequentially – smoothly increasing the gain by placing a decreasing impedance in parallel with  $R_{g_o}.$  Additional RC pairs can be added to improve the approximation. In this circuit, the maximum high frequency current in the gain setting network will be set by  $R_{g_1}||R_{g_o}.$  It is important to check that  $I_{TAIL}$  is not exceeded when a high frequency input differential signal is placed across this  $R_{g_1}||R_{g_o}$  minimum impedance.

Figure 7: Wideband, Equalizing, Differential Cable Receiver with Adjustable Gain

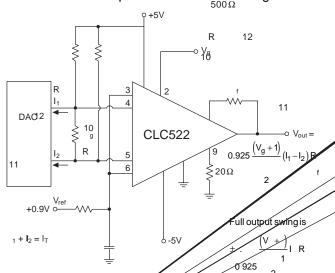

# **DAC Transimpedance Interface**

Most high speed DAC's are complementary current output devices where the output is actually sinking current into the DAC. From a fixed maximum current available, the digital codes acts to steer how this total current is split between the two outputs. By pulling these two currents directly out of the CLC522 buffer outputs (pins 4 and 5), the CLC522 can be easily used to perform an adjustable gain complementary current to single ended voltage conversion. An example of this is shown in Figure 8.

Figure 8: DAC Differential Transimpedance Interface

http://www.mational.com

This circuit actually implements a very wideband multiplying DAC function. Instead of scaling the IT current internal to the DAC, this circuit uses the CLC522's  $V_g$  input to scale the DAC current that goes to the CLC522's transimpedance stage. It is important to note that for  $V_g = 0$  the output is not at zero nor does the output polarity invert as  $V_g$  goes < 0V. This is then a multiplying DAC in the sense that  $V_g$  can be used to compress the gain from the DAC codes to output voltage swing.

This approach provides an exceptionally low impedance load with no compliance voltage problems at the output of the DAC. The +0.9V DC reference on the buffer inputs compensates for a 0.9V drop from the buffer inputs to their outputs and allows the DAC currents sources to drive into a 0 volt low impedance load. The two 5k resistors to the +V $_{\rm CC}$  supply provide a 1mA bias to compensate part of the internal 1.8mA I $_{\rm TAIL}$ . This increases the maximum value allowed for the DAC output current to 3mA before non-linear internal limiting will occur in the CLC522. Rg should be set to relatively high value but plays no role in setting the signal gain in this case.

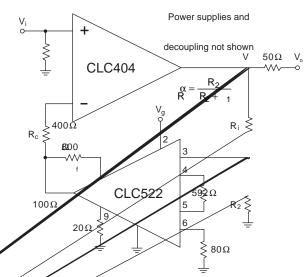

# Using the CLC522 as a Feedback Element for Another Op Amp

One approach to extending the gain adjustment range for the CLC522 is to imbed the adjustable gain stage as the feedback element for either a voltage or current feedback op amp. Figure 9 shows this topology along with some example component values using the CLC404 current feedback op amp.

Figure 9: Using the CLC522 as the a Feed Element

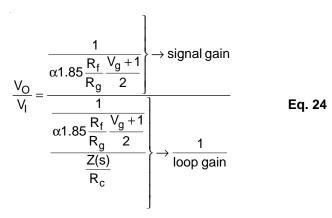

This circuit offers several advantages and disadvantages (over simply using the CLC522 as an adjustable gain stage) in applications where it is desired to hold a constant peak to peak output swing. The principal advantage for this circuit is that the peak input swing into the CLC522 is constant. This eliminates the gain adjust range limitations discussed earlier. Equation 24 shows the overall transfer function ignoring the bandwidth limitations of the CLC522.

$5k\Omega$

$Z(s) \rightarrow$  Open loop transimpedance gain for the forward path current feedback op amp

This transfer function shows that the forward gain now depends on the inverse of the gain through the CLC522. Hence, to get high forward gain, the CLC522 needs to be operating as an attenuator. Some of this attenuation is provided by the resistor divider ( $\alpha$ ) from the output of the forward op amp. The linear gain adjust characteristic of the CLC522 has been transformed to a 1/x type transfer gain. If Vg were adjusted to -1, shutting the CLC522 off, the forward path will go open loop and have a gain equal to Z(s)/R<sub>c</sub>.

Equation 24 also shows that the loop gain equation has become a purely voltage feedback type characteristic showing a gain-bandwidth product – even when using a current feedback op amp. A current feedback forward stage is preferred, however, to provide superior large signal swing and to allow easy frequency response compensation through adjusting the value of  $R_{\rm c}$ . The input referred noise has been increased since it now becomes the output noise of the CLC522. However, as the input peak to peak signal decreases, the gain is increased by decreasing the CLC522 gain. This will have the effect of decreasing the input referred noise as the input signal level decreases.

#### **Voltage Squaring Circuit**

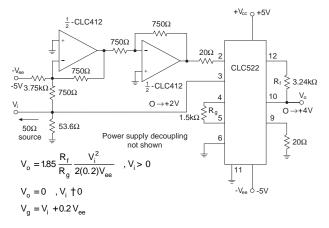

Figure 10 shows a way of using the CLC522 to square an input signal voltage. The specific values used in this example will scale the output by a 2X multiple of Vi^2.

Figure 10: High Speed Voltage Squaring Circuit

This circuit applies the signal input to both the gain adjust pin and the non-inverting input pin. A wideband dual amplifier, the CLC412, is used to both sum the signal and a correction factor for the -V $_{\rm EE}$  supply in an inverting summing stage and to invert the signal again to the correct polarity for driving the V $_{\rm g}$  input of the CLC522. Stepping through the algebra to get V $_{\rm o}/\rm V_{\rm i}$  yields -

The signal gain including the dependence on the negative supply is:

$$V_o/V_i i = 1.85 * (Rf/Rg) * 0.5 * (1 - V_q/(.2 * V_{EE}))$$

Substituting in  $V_g = V_i + 0.2 * V_{EE}$  from Figure 10

$$\frac{V_o}{V_i} = 1.85 \frac{R_f}{R_g} \frac{V_i}{0.2V_{EE}}$$

$$V_o = 1.85 \frac{R_f}{R_g} \frac{V_i^2}{2(0.2)|V_{EE}|}, V_i > 0$$

$$V_o = 0, V_i \le 0$$

This circuit will square the input voltage for  $V_i > 0$ , but will yield 0V output for  $V_i < 0$ .

# 4 - Quadrant Multiplier

The CLC522 is principally intended as a 2-quadrant multiplier. Although bipolar inputs at either of the two buffer inputs will pass on to the output as bipolar signals, inputs into the  $V_{\rm g}$  input can only compress the gain for the signal channel inputs. In other words, with a fixed DC signal channel input, bipolar inputs on the  $V_{\rm g}$  channel do not generate bipolar output signals. However, by summing the non-inverting input buffer signal directly into the inverting input of the output amplifier (in parallel with the internal gain adjusted signal), a 4 - quadrant multiplier can be emulated. Figure 11 shows this application along with the design equations -

Figure 11: High-Speed Voltage Squaring

This circuit is particularly suitable at lower frequencies (< 5MHz). As the frequency increases, unequal delays between the internal and external signal paths reduce its effectiveness. In a mixer application, this translates into a decreased LO suppression at higher frequencies.

# Wide Dynamic Range 1/2 Wave Rectifier

If a bipolar signal is applied to the signal inputs of the CLC522 and that same signal is used to toggle a comparator that switches the gain control channel from maximum gain to full attenuation, a simple and effective 1/2 wave rectifier may be implemented. Figure 12 shows an example of this application.

Figure 12: 1/2 Wave Rectifier

Most diode based rectifier circuits suffer from a signal level dependent frequency response. The circuit of Figure 12 relies upon the polarity of the current into the inverting input of a high speed current feedback clipping amplifier (the CLC501) to switch the CLC522's gain control input from full on to full off. In this case, negative 1/2 cycle of a sinusoidal signal cause the CLC501 to drive to the positive clamp passing those negative 1/2 cycles on to the CLC522 output. Since the input has been connected up to the inverting buffer side, these negative 1/2 cycles are passed to the output of the CLC522 as positive 1/2 cycles.

The signal amplitude range that will produce good rectified outputs depends only on how good the comparator is driving the gain adjust input. In the circuit of Figure 12, the full open loop gain of the CLC501 is available to respond to a switch in the polarity of the current into its inverting node. An alternative high speed voltage controlled comparator could also be used. The speed of operation is primarily limited by how fast the comparator can respond to a change in polarity at its input.

# Adjustable Cutoff, Single Pole, Low Pass Filter

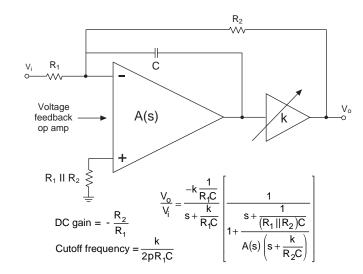

By putting the adjustable gain CLC522 inside the loop of an integrator stage, a variable cutoff low pass filter may be implemented. Figure 13 shows the generalized analysis of this technique.

Figure 13: Tuneable Single Pole Low Pass Filter

This circuit implements an inverting gain stage with a DC gain of  $-R_2/R_1$ . Varying K has the effect of raising and lowering the open loop forward gain which has been given a pure integrator shape by the input voltage feedback op amp. Shifting the open loop gain up and down will vary the closed loop bandwidth when the feedback gain is fixed by  $R_1$  and  $R_2$ . A specific example of this circuit is shown in Figure 14.

Figure 14: Adjustable Bandwidth Amplifier

This particular configuration provides a gain of -2 with a 10MHz cutoff when the CLC522 is at maximum gain ( $V_g = 1$ ). As the gain is decreased the bandwidth will decrease directly. For a fixed output voltage swing, Vopp, decreasing the bandwidth by dropping the CLC522 gain will increase the voltage swing at the input of the CLC522. Given this desired  $V_{opp}$ , the available range of bandwidth reduction, before the input range of the CLC522 is exceeded, will be set by  $2 * I_{TAIL} * R_f/V_{opp} = BW_{max}/BW_{min}$  (Please see the discussion of usable gain adjust range).

# CLC522 Typical Performance ( $T_A=25^{\circ}C$ , $V_{cc}=\pm5V$ , $A_v=+10V/V$ , $R_f=100\Omega$ , $V_g=1.1$ , unless noted)

# CLC522 Typical Performance ( $T_A=25^{\circ}C$ , $V_{cc}=\pm5V$ , $A_v=+10V/V$ , $R_f=100\Omega$ , $V_q=1.1$ , unless noted)

| CLC522 Electrical Characteristics ( $\pm V_{cc} = \pm 5V$ , $R_L = 100\Omega$ , $R_f = 1k\Omega^1$ , $R_g = 182\Omega^1$ , $A_{Vmax} = +10V/V$ , $V_g = +1.1V$ )                                                                                                                                                                                                                            |                                                                                                              |                                                                                        |                                                                                          |                                                                                                |                                                                               |                                                                                          |                                                                                              |                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------|

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                   | CONDITIONS                                                                                                   | TYP                                                                                    |                                                                                          | MAX & MIN                                                                                      | N RATING                                                                      | SS                                                                                       | UNITS                                                                                        | SYMBOL                        |

| Ambient Temperature Ambient Temperature                                                                                                                                                                                                                                                                                                                                                     | CLC522AJ/AI<br>CLC522A8                                                                                      | +25¡C<br>+25¡C                                                                         | 0¡C<br>70¡C                                                                              | -40¡C<br>-55¡C                                                                                 | +25¡C<br>+25¡C                                                                | +85¡C<br>+125¡C                                                                          |                                                                                              |                               |

| FREQUENCY RESPONSE small signal bandwidth  gain control bandwidth (V <sub>in</sub> =0.2V)                                                                                                                                                                                                                                                                                                   |                                                                                                              | 165<br>150<br>165                                                                      | 115<br>95<br>115                                                                         | 110<br>100<br>110                                                                              | 120<br>100<br>120                                                             | 110<br>90<br>110                                                                         | MHz<br>MHz<br>MHz                                                                            | SSBW<br>LSBW                  |

| gain flatness peaking rolloff DC-30MHz peaking                                                                                                                                                                                                                                                                                                                                              | V <sub>out</sub> < 0.5V <sub>pp</sub><br>DC-30MHz<br>0.05<br>DC-200MHz                                       | 0<br>0.25<br>0                                                                         | 0.1<br>0.4<br>0.5                                                                        | 0.1<br>0.25<br>0.5                                                                             | 0.1<br>0.25<br>0.5                                                            | 0.1<br>dB<br>0.7                                                                         | dB<br>GFR<br>dB                                                                              | GFPL<br>GFPH                  |

| rolloff DC-60MHz<br>linear phase deviation<br>feedthrough (at max. attenuation)                                                                                                                                                                                                                                                                                                             | 0.3<br>DC-60MHz<br>30MHz                                                                                     | 1.0<br>0.5<br>-62                                                                      | 1.3<br>1.1<br>-57                                                                        | 1.0<br>1.2<br>-57                                                                              | 1.0<br>1.0<br>-57                                                             | dB<br>1.2<br>-57                                                                         | deg<br>dB                                                                                    | LPD<br>FDT                    |

| TIME DOMAIN RESPONSE rise and fall time settling time to -0.1% overshoot slew rate                                                                                                                                                                                                                                                                                                          | 0.5V step<br>5.0V step<br>2.0V step<br>0.5V step<br>4V step                                                  | 2.2<br>3.0<br>12<br>2<br>2000                                                          | 3.0<br>5.0<br>18<br>15<br>1400                                                           | 2.9<br>5.0<br>18<br>15<br>1400                                                                 | 2.9<br>5.0<br>18<br>15<br>1400                                                | 3.2<br>5.0<br>18<br>15<br>1400                                                           | ns<br>ns<br>ns<br>%<br>V/µsec                                                                | TRS<br>TRL<br>TSP<br>OS<br>SR |

| DISTORTION AND NOISE PERFORM 2nd harmonic distortion 3rd harmonic distortion equivalent output noise noise floor spot noise                                                                                                                                                                                                                                                                 | ORMANCE<br>2V <sub>pp</sub> , 20MHz<br>2V <sub>pp</sub> , 20MHz<br>(see noise model)<br>1-200MHz<br>1-200MHz | -50<br>-65<br>-132<br>58                                                               | -44<br>-56<br>-129<br>65                                                                 | -44<br>-58<br>-130<br>62                                                                       | -44<br>-58<br>-130<br>62                                                      | -44<br>-54<br>-129<br>68                                                                 | dBc<br>dBc<br>dBm <sub>1Hz</sub><br>nV/√Hz                                                   | HD2<br>HD3<br>SNF<br>INV      |

| static DC PERFORMANCE integral signal nonlinearity gain control nonlinearity V <sub>g</sub> input bias current V <sub>g</sub> average temperature coefficient gain error output offset voltage average temperature coeffi input bias current average temperature coeffi input offset current average temperature coeffi power supply sensitivity common mode rejection ratio supply current | A <sub>Vmax</sub> = 10V/V<br>icient<br>icient                                                                | 0.04<br>0.5<br>15<br>125<br>-0.0<br>25<br>100<br>9<br>65<br>0.2<br>5<br>10<br>70<br>46 | 0.1<br>2.2<br>47<br>300<br>-0.5<br>95<br>350<br>26<br>175<br>3.0<br>30<br>40<br>59<br>62 | 0.1<br>3.0<br>82<br>600<br>+0.5,-1.0<br>120<br>400<br>45<br>275<br>4.0<br>40<br>40<br>59<br>63 | 0.1<br>2.0<br>38<br><br>-0.5<br>85<br><br>21<br><br>2.0<br><br>40<br>59<br>61 | 0.1<br>2.5<br>38<br>210<br>-0.5<br>90<br>300<br>21<br>125<br>2.0<br>20<br>40<br>59<br>61 | %<br>%<br>μA<br>nA/¡C<br>dB<br>mV<br>μV/¡C<br>μA<br>nA/¡C<br>μA<br>nA/¡C<br>MV/V<br>dB<br>mA | DIBI<br>CMRR<br>ICC           |

| MISCELLANEOUS PERFORMAN  Vin signal inputs  buffer tail current (I <sub>TAIL</sub> = max. R <sub>g</sub> of Vin common mode voltage range V <sub>g</sub> control input  V <sub>g</sub> control voltage tolerance  output impedance output voltage range output current                                                                                                                      | resistance<br>capacitance                                                                                    | 1500<br>1.0<br>1.8<br>-2.2<br>100<br>1.0<br>990-0<br>-975-0<br>0.1<br>-4.0<br>-70      | 450<br>2.0<br>1.26<br>-1.2<br>30<br>2.0<br>-60<br>-80<br>0.3<br>-3.6<br>-40              | 175<br>2.0<br>1.37<br>-1.4<br>15<br>2.0<br>-60<br>-80<br>0.6<br>-3.5<br>-25                    | 650<br>2.0<br>1.37<br>-1.2<br>38<br>2.0<br>-60<br>-80<br>0.2<br>-3.7<br>-47   | 650<br>2.0<br>1.15<br>-1.2<br>38<br>2.0<br>-60<br>-80<br>0.2<br>-3.7<br>-47              | kΩ<br>pF<br>mA<br>V<br>kΩ<br>pF<br>mV<br>mV<br>Ω<br>V                                        | RIN<br>CIN<br>RO<br>VO<br>IO  |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as Noted. Outgoing quality levels are determined from tested parameters.

This page intentionally left blank.

# **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at **1-800-272-9959** or fax **1-800-737-7018**.

#### **Life Support Policy**

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

# National Semiconductor Corporation

1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

#### National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 E-mail: europe.support@nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Francais Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80

#### National Semiconductor Hong Kong Ltd.

2501 Miramar Tower 1-23 Kimberley Road Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

#### National Semiconductor Japan Ltd.

Tel: 81-043-299-2309 Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.