# The NS16550A: UART Design and Application Considerations

#### **BACKGROUND**

UARTs like other system components have evolved for many years to become faster, more integrated and less expensive. The rise in popularity of the personal computer with its focus and competition primarily centered on an architecture introduced by IBM®, has driven both UART performance and software compatibility issues. As transmission rates have increased, the amount of time the CPU has for other tasks while handling an active serial channel has been sharply reduced. One byte of data received at 1200 baud (8.3 ms) is received in  $1/_{16}$ th the time at 19.2 kbaud (520  $\mu$ s). Software compatibility among the PC-based UARTs is critical due to the thousands of existing programs which use the serial channel and the new programs continually being offered

Higher baud rates and compatibility requirements influence new UART designs. These two constraints result in UARTs that are capable of higher data rates, increasingly independent of CPU intervention and providing more autonomous features, while maintaining software compatibility. These development paths have been brought together in a new UART from National Semiconductor designated the NS16550A.

The NS16550A has all of the registers of its two predecessor parts (INS8250 and NS16450), so it can run all existing IBM PC, XT, AT, RT and compatible serial port software. In addition, it has a programmable mode which incorporates new high-performance features. Of course, all of these advanced features are useful in any asynchronous serial communications application regardless of the host architecture.

The reader is assumed to be familiar with the standard features of the NS16450, so this paper will concentrate mainly on the new features of the NS16550A. If the reader is unfamiliar with these UARTs it is advisable to start by reading their data sheets.

The first section reviews some of the design considerations and the operation of the NS16550A advanced features. The second section shows an NS16550A initialization routine written in 80286 assembly code with an explanation of the routine. The third section gives a detailed example of communications drivers written to interface two NS16550As on individual boards. These drivers are written for use with National Semiconductor's DB32032 evaluation boards, but can be ported to any NS32032-based system containing an NS32202 (ICU).

# 1.0 Design Considerations and Operation of the New UART Features

In order to optimize CPU/UART data transactions, the UART design takes into consideration the following concernitors

GNXTM is a trademark of National Semiconductor Corporation. IBM® is a registered trademark of International Business Machines Corporation. VAXTM is a trademark of Digital Equipment Corporation. 80286TM is a trademark of Intel Corporation. National Semiconductor Application Note 491 Martin S. Michael Daniel G. Durich July 1987

- The CPU is usually much faster than the UART at transferring data. A high speed CPU could transfer a byte of data to/from the UART in a minimum of 280 ns. The UART would take over 1800 times longer to transmit/receive this data serially if it were operating at 19.2 kbaud.

- There is a finite amount of wasted CPU time due to software overhead when stopping its current task to service the UART (context switching overhead).

- 3. The CPU may be required to complete a certain portion of its current task in a multitasking system before servicing the UART. This delay is the CPU latency time associated with servicing the interrupt. The amount of time that the receiver can accept continuous data after it requests service from the CPU constrains CPU latency time.

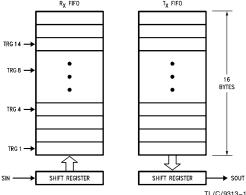

The design constraints listed above are met by adding two FIFOs and specialized transmitter/receiver support circuitry to the existing NS16450 design. The FIFOs are 16 bytes deep—one holds data for the transmitter, the other for the receiver (see *Figure 1*). Similarity between the FIFOs stops with their size, as each has been customized for special

FIGURE 1. Rx and Tx FIFOs

transmitter or receiver functions. Each has support circuitry to minimize software overhead when handling interrupts. The NS16550A **receiver** optimizes the CPU/UART data transaction via the following features:

- The depth of the Receiver (Rx) FIFO ensures that as many as 16 characters will be ready to transfer when the CPU services the Rx interrupt. Therefore, the CPU transfer rate is effectively buffered from the serial data rate.

- 2. The program can select the number of bytes required in the Rx FIFO (1, 4, 8 or 14) before the UART issues an interrupt. This allows the software to modify the interrupt trigger levels depending on its current task or loading. It also ensures that the CPU doesn't continually waste time switching context for only a few characters.

The Rx FIFO will hold 16 bytes regardless of which trigger level the CPU selects. This makes allowances for a variety of CPU latency times, as the FIFO continues to fill after the interrupt is issued.

The NS16550A **transmitter** optimizes the CPU/UART data transaction via the following features:

- The depth of the Transmitter (Tx) FIFO ensures that as many as 16 characters can be transferred when the CPU services the Tx interrupt. Once again, this effectively buffers the CPU transfer rate from the serial data rate

- The Transmitter (Tx) FIFO is similar in structure to FIFOs the user may have previously set up in RAM. The Tx depth allows the CPU to load 16 characters each time it switches context to the service routine. This reduces the impact of the CPU time lost in context switching.

- Since a time lag in servicing an asynchronous transmitter usually has no penalty, CPU latency time is of no concern to transmitter operation.

#### **TX AND RX FIFO OPERATION**

The Tx portion of the UART transmits data through SOUT as soon as the CPU loads a byte into the Tx FIFO. The UART will prevent loads to the Tx FIFO if it **currently** holds 16 characters. Loading to the Tx FIFO will again be enabled as soon as the next character is transferred to the Tx shift register. These capabilities account for the largely autonomous operation of the Tx.

The UART starts the above operations typically with a Tx interrupt. The NS16550A issues a Tx interrupt whenever the Tx FIFO is empty and the Tx interrupt is enabled, except in the following instance. Assume that the Tx FIFO is empty and the CPU starts to load it. When the first byte enters the FIFO, the Tx FIFO empty interrupt will transition from active to inactive. Depending on the execution speed of the service routine software, the UART may be able to transfer this byte from the FIFO to the shift register before the CPU loads another byte. If this happens, the Tx FIFO will be empty again and typically the UART's interrupt line would transition to the active state. This could cause a system with an interrupt control unit to record a Tx FIFO empty condition, even though the CPU is currently servicing that interrupt. Therefore, after the first byte has been loaded into the FIFO the UART will wait one serial character transmission time before issuing a new Tx FIFO empty interrupt.

This one character Tx interrupt delay will remain active until at least two bytes have been loaded into the FIFO, concurrently. When the Tx FIFO empties after this condition, the Tx interrupt will be activated without a one character delay. Rx support functions and operation are quite different from those described for the transmitter. The Rx FIFO receives data until the number of bytes in the FIFO equals the selected interrupt trigger level. At that time if Rx interrupts are enabled, the UART will issue an interrupt to the CPU. The Rx FIFO will continue to store bytes until it holds 16 of them. It will not accept any more data when it is full. Any more

data entering the Rx shift register will set the Overrun Error flag. Normally, the FIFO depth and the programmable trigger levels will give the CPU ample time to empty the Rx FIFO before an overrun occurs.

One side-effect of having a Rx FIFO is that the selected interrupt trigger level may be above the data level in the FIFO. This could occur when data at the end of the block contains fewer bytes than the trigger level. No interrupt would be issued to the CPU and the data would remain in the UART. To prevent the software from having to check for this situation the NS16550A incorporates a timeout interrupt.

The timeout interrupt is activated when there is at least one byte in the Rx FIFO, and neither the CPU nor the Rx shift register has accessed the Rx FIFO within 4 character times of the last byte. The timeout interrupt is cleared or reset when the CPU reads the Rx FIFO or another character enters if

These FIFO related features allow optimization of CPU/UART transactions and are especially useful given the higher baud rate capability (256 kbaud). However, in order to eliminate most CPU interactions, the UART provides DMA request signals. Two DMA modes are supported: single-transfer and multi-transfer. These modes allow the UART to interface to higher performance DMA units, which can interleave their transfers between CPU cycles or execute multiple byte transfers.

In single-transfer mode the receiver DMA request signal (Rx RDY) goes active whenever there is at least one character in the Rx FIFO. It goes inactive when the Rx FIFO is empty. The transmitter DMA request signal (Tx RDY) goes active when there are no characters in the Tx FIFO. It goes inactive when there is at least one character in the Tx FIFO. Therefore, in single-transfer mode active and inactive DMA signals are issued on a one byte basis.

In multi-transfer mode Rx RDY goes active whenever the trigger level or the timeout has been reached. It goes inactive when the Rx FIFO is empty. Tx RDY goes active when there is at least one unfilled position in the Tx FIFO. It goes inactive when the Tx FIFO is completely full. Therefore in multi-transfer mode active and inactive DMA signals are issued as the FIFO fills and empties. With 2 DMA channels (one for each Rx and Tx) assigned to it, the NS16550A could run somewhat independently of the CPU when the DMA unit transfers data composed of blocks with check-

#### SYSTEM OPERATION: THE NS16550A VS THE NS16450

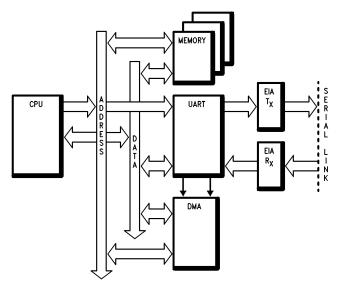

Consider the typical system interface block diagram in Figure 2. This is a simple diagram, but it includes all of the components that typically interact with a UART. The advantages of the NS16550A over the NS16450 can be illustrated by comparing some of the system constraints when each UART is substituted into this basic system.

Both RS-232C and RS-422A interfaces can be used with either UART, however, the NS16550A can drive these interfaces up to 256 kbaud. Regarding the RS-422A specifica-

FIGURE 2. Typical System Interface

TL/C/9313-2

tion (max. 10 Mbaud) this is significantly faster than the NS16450 (max. 56 kbaud).

The NS16450 has no DMA request signals, so the DMA unit would not interact with the NS16450. The NS16550A, however, has DMA request signals and two modes of data transfer, as previously described, to interface with a variety of DMA units.

The greatest advantages of the NS16550A over the NS16450 are seen when considering the CPU/UART interface. Some characteristics of the transactions occurring between the CPU and the UART were previously cited. However, optimizing these transactions involves two issues:

- Decreasing the amount of time the CPU interacts with the LIART.

- Increasing the amount of data transferred between the CPU and UART during their interaction time.

These optimization criteria are directly opposed to each other, but various features on the NS16550A have improved both

One of the more obvious ways to decrease the CPU/UART interaction time is to decrease the time it takes for the transaction to occur. The NS16550A has an access cycle time that is almost 25% shorter than the NS16450. In addition, other timing parameters were made faster to simplify high speed CPU interactions.

The actual software required to transfer the data between the CPU and the UART is a small percentage of that required to support this transfer. However, each time a transfer occurs in the NS16450, this support software (overhead) must also be executed. With the NS16550A each time the UART needs service the CPU can theoretically transfer 16 bytes while only running through its overhead once. Tests have shown that this will increase the performance by a factor of 5 at the system level over the NS16450.

Another time savings for the CPU is a new feature of the UART interrupt structure. Unlike most other UARTs with Rx

FIFOs, the NS16550A will issue an interrupt when there are characters below the interrupt trigger level after a preset time delay. This saves the extra time spent by the CPU to check for bytes that are at the end of a block, but won't reach the interrupt level.

Since the NS16550A register set is identical to the NS16450 on power-up, all existing NS16450 software will run on it. The FIFOs are only enabled under program control.

All of this added performance is not without some trade-offs. Two of the NS16450 pins, no connect (NC) and chip select out (CSOUT) have been replaced by the RXRDY and TXRDY pins. Most serial cards that currently use the NS16450 don't use these pins, so in those situations the NS16550A could be used as a plug-in upgrade. The software drivers for the NS16550A operating in FIFO mode need to be a little more sophisticated than for the NS16450. This will not cause a great penalty in CPU operating time as there is only one additional UART register to program and one to check during the initialization. One additional service routine is required to handle Rx timeout interrupts. This routine does not execute, except during intermittent transmissions or as described above.

All of these speed improvements and allowances for software constraints will make the NS16550A an optimal UART for both multi-tasking systems and multiport systems. Multitasking systems benefit from the increased time and flexibility offered to the CPU during context switching. Multiport systems, such as terminal concentrators, benefit from the on-board FIFOs and relatively autonomous functions of the UART.

# SYSTEM INTERRUPT GENERATION

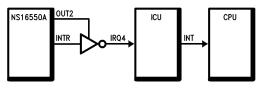

As a prelude to the topic of the next section (80286TM-based system initialization) a review of a typical PC hardware interrupt path is given. This concerns only the interrupt path between the UART and the CPU (see Figure 3).

FIGURE 3. Typical PC Interrupt System Hardware

TL/C/9313-3

In order to enable interrupts from the UART to the CPU each hardware device must be correctly initialized. While initializing the hardware path, CPU interrupts are turned off to avoid false interrupts from this path. This initialization should be as short as possible to avoid other devices "stacking up" interrupts during this time.

After the NS16550A is initialized the bits 0-3 in the Interrupt Enable Register (IER) are set enabling all UART interrupts. Also, bit 3 in the Modem Control Register (MCR) is set to enable the buffer between the UART and the ICU.

The ICU has bit 4 of its Interrupt Mask Register (IMR) cleared, allowing interrupts occuring on IRQ4 to be transferred to the CPU via the group interrupt (INT). Finally, CPU interrupts are enabled again via the STI instruction.

The programmer should be aware that the ICU will be initialized for edge-triggered interrupts and that the UART always produces level active interrupts. This allows the system to get into a situation where the UART has multiple interrupts pending (signaled via a constantly high INTR), but the ICU fails to respond because it expects an edge for each pending interrupt. To avoid this situation, the programmer should disable all UART interrupts via the IER when entering each UART interrupt service routine and then reenable all UART interrupts that are to be used just before exiting each interrupt service routine.

#### SUMMARY

Up to this point the features of the NS16550A have been described, some of the design goals that resulted in these features have been reviewed, and a comparison has been given between it and the NS16450. Increases in bus speed and specialized functions make this part both faster from the hardware point of view and more efficient from the software point of view.

# 2.0 NS16550A Initialization

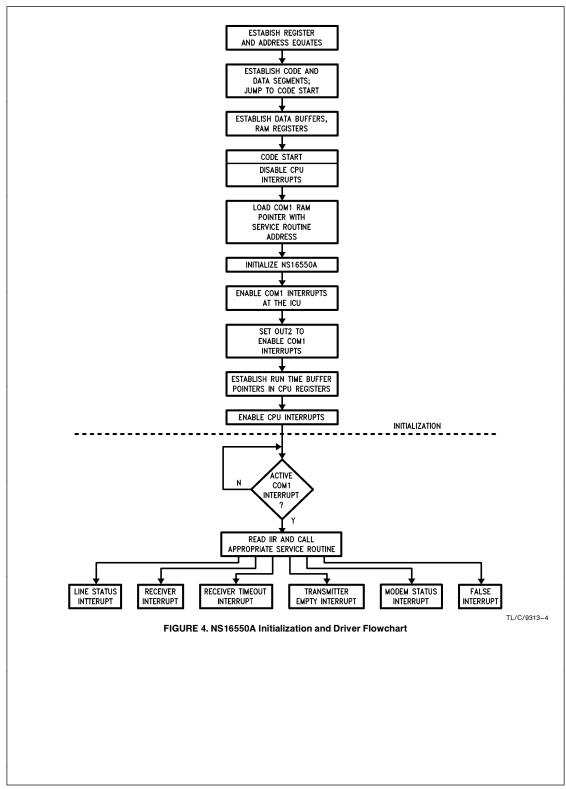

This initialization can be used on any 80286-based system; it enables both FIFOs and all interrupts on the UART. Additional procedures would have to be written to actually transfer data and service interrupts. These procedures would be similar in form to the 32000-based example in the next section, but the code would be different. The general flow of the initialization is shown in *Figure 4* and described below.

# **DETAILED SOFTWARE DESCRIPTION**

The first block in the initialization establishes abbreviations for the NS16550A registers and assigns addresses to them. The next three blocks establish code and data segments for the 80286. After jumping to the code start, the program disables CPU interrupts (CLI) until it has finished the initialization routine. Other interrupts may be active while CPU inter-

rupts are masked, so the section of code following CLI should be as short as possible. The next block replaces the existing COM1 interrupt vector with the address of NS16550A interrupt handler (INTH in this case).

Initialization of the NS16550A is similar to the NS16450. except that there is one additional register to program which controls the FIFOs (Refer to the datasheet for a complete description). The sequence shown here sets bit 7 (DLAB) of the line control register (LCR), which enables access to the baud rate generator divisor. The divisor programmed is 0006 (19.2 kbaud) in this example. Programming the LCR again resets bit 7 (allowing access to the operational registers) and programs each frame for 7 data bits, one stop bit and even parity. The additional register that needs to be programmed in the NS16550A is the FIFO control register (FCR). The FCR data is 1100 0001. Bits 6 and 7 set the Rx FIFO interrupt trigger level at 14 characters. Bits 5 and 4 are reserved. Bit 3 keeps the DMA signal lines in mode 0. Setting bits 2 and 1 clear the Tx and Rx FIFOs, but this is done automatically when the FIFOs are first enabled by setting bit 0. Bit 0 of the FCR should ALWAYS BE SET whenever changes are to be made to the other bits of the FCR and the UART is to remain in FIFO Mode. When the FIFOs on the NS16550A are enabled bits 6 and 7 in the Interrupt Identification Register are set. Thus the program can distinguish between an NS16450 and an NS16550A, taking advantage of the FIFOs.

Sending a 0F to the Interrupt Enable Register enables all UART interrupts. The next two register accesses, reading the Line Status Register and the Modem Status Register, are optional. They are conservatively included in this initialization in order to defeat false interrupt indications in these registers caused by noise on the external lines.

The next block of code enables the interrupt signal to go beyond the UART through the system hardware. In many popular 80286-based personal computers, an interrupt control unit (ICU) has its mask register at I/O address 21H. To enable interrupts through this ICU for COM1 without disturbing other interrupts, the Interrupt Mask Register (IMR) is read. This data is combined with 1110 1111 via an AND instruction to unmask the COM1 interrupt and then loaded it back to the IMR. On these personal computers there is also a buffer on the interrupt line between the UART and ICU. This buffer is enabled by setting the OUT2 bit of the MODEM Control Register in the UART.

Before enabling CPU interrupts (STI) pointer registers to the data buffers of each service routine are loaded. After enabling CPU interrupts this program jumps to a holding loop to wait for an interrupt, whereas most programs would continue initializing other devices or jump to the system loop.

```

TITLE 550APP.ASM - NS16550A INITIALIZATION

;ESTABLISH NS16550A REGISTER ADDRESS/DATA EQUATES

:******** UART REGISTERS ************

:

rxd

EQU 3F8H

RECEIVE DATA REG

EQU 3F8H

txd

TRANSMITT DATA REG

ier EQU 3F9H

;INTERRUPT ENABLE REG

dll EQU 3F8H

;DIVISOR LATCH LOW

dlh EQU 3F9H

;DIVISOR LATCH HIGH

iir EQU 3FAH

;INTERRUPT IDENTIFICATION REG

for EQU 3FAH

;FIFO CONTROL REG

lcr EQU 3FBH

;LINE CONTROL REG

mcr EQU 3FCH

;MODEM CONTROL REG

lsr EQU 3FDH

;LINE STATUS REG

msr EQU 3FEH

;MODEM STATUS REG

scr EQU 3FFH

;SCRATCH PAD REG

bufsize EQU 7CFH

;TX AND RX BUFFER SIZE

dosrout EQU 25H

;INTERRUPT NUMBER (OCH = COM1)

;ICU INTERRUPT ENABLE MASK

;DIVISOR LATCH ACCESS CODE

;LOWER DIVISOR

;UPPER DIVISOR

;DOS ROUTINE SPECIFICATION

intnum EQU OCH

icumask EQU OEFH

divacc EQU 80H

lowdiv EQU 06H

uppdiv EQU 00H

;DLAB = 0, 7 BITS, 1 STOP, EVEN

;FIFOS ENABLED, TRIG = 14, DMA MODE = 0

dataspc EQU 1AH

fifospc EQU OC1H

setout2 EQU 08H

;SETTING OUT2 ENABLES INTRS TO THE ICU

;UART INTERRUPT ENABLE MASK

intmask EQU OFH

;******* ESTABLISH CODE AND DATA SEGMENTS ***********

cseg

SEGMENT PARA PUBLIC "code"

ORG 100H

ASSUME CS:cseg, DS:cseg

INIT:

PUSH

POP

DS

JMP

START

;****** ESTABLISH DATA BUFFERS AND RAM REGISTERS *******

msflag DB

txflag DB

0

sbuf DB bufsize DUP ("S") ; STRING BUFFER

rbuf DB bufsize DUP ("R") ; RECEIVE BUFFER

sbufe EQU sbuf + bufsize ; END OF STRING BUFFER

rbufe EQU

rbuf + bufsize

; END OF RECEIVE BUFFER

START:

CT<sub>1</sub>T

;>>> DISABLE CPU INTERRUPTS <<<

```

```

;***** LOAD NEW INTERRUPT SERVICE ROUTINE POINTER FOR COM1 ***

PUSH

;SAVE EXISTING DATA SEG

DS

MOV

AH, dosrout

:DESIGNATE FUNCTION NUMBER

AL, intnum

MOV

:DESIGNATE INTERRUPT

PUSH CS

:ALIGN CODE SEG

POP

DS

:WITH DATA SEG

DX, OFFSET INTH ; SPECIFY SERVICE ROUTINE OFFSET

VOM

INT

21H

;REPLACE EXISTING INTR VECTOR

;RESTORE CURRENT DATA SEG

POP

DS

;This enables both FIFOs for data transfers at 19.2 kbaud using

;7 bit data, 1 stop bit and even parity. The \ensuremath{\mathtt{Rx}} FIFO interrupt

;trigger level is set at 14 bytes.

;SET-UP ACCESS TO DIVISOR LATCH

VOM

AL, divacc

VOM

DX.lcr

DX,AL

OUT

MOV

AL, lowdiv

;LOWER DIVISOR LATCH, 19.2 kbaud

MOV

DX,dll

DX,AL

OUT

;UPPER DIVISOR LATCH

MOV

AL,uppdiv

MOV

DX.dlh

OUT

DX.AL

MOV

AL, dataspc

;DLAB = 0, 7 BITS, 1 STOP, EVEN

MOV

DX.lcr

OUT

DX,AL

AL,fifospc

MOV

;FIFOS ENABLED, TRIGGER = 14,

MOV

DX,fcr

:DMA MODE = 0

OUT

DX.AL

MOV

AL, intmask

:ENABLE ALL UART INTERRUPTS

MOV

DX,ier

OUT

DX,AL

MOV

DX,1sr

;READ THE LSR TO CLEAR ANY FALSE

IN

AL,DX

;STATUS INTERRUPTS

MOV

DX,msr

;READ THE MSR TO CLEAR ANY FALSE

IN

AL,DX

;MODEM INTERRUPTS

IN

AL,21H

;CHECK IMR

;ENABLE ALL EXISTING AND COM1

AND

AL,icumask

OUT

21H.AL

;SET OUT2 TO ENABLE INTR

MOV

AL, setout2

MOV

DX.mcr

OUT

DX,AL

;******* ESTABLISH RUN TIME BUFFER POINTERS IN REGISTERS ***

MOV

SI, OFFSET sbuf

DI.OFFSET rbuf

MOV

VOM

BX,OFFSET sbuf

VOM

BP,OFFSET rbuf

STI

;>>> ENABLE CPU INTERRUPTS <<<

```

# 3.0 Board to Board Communications with the NS16550A

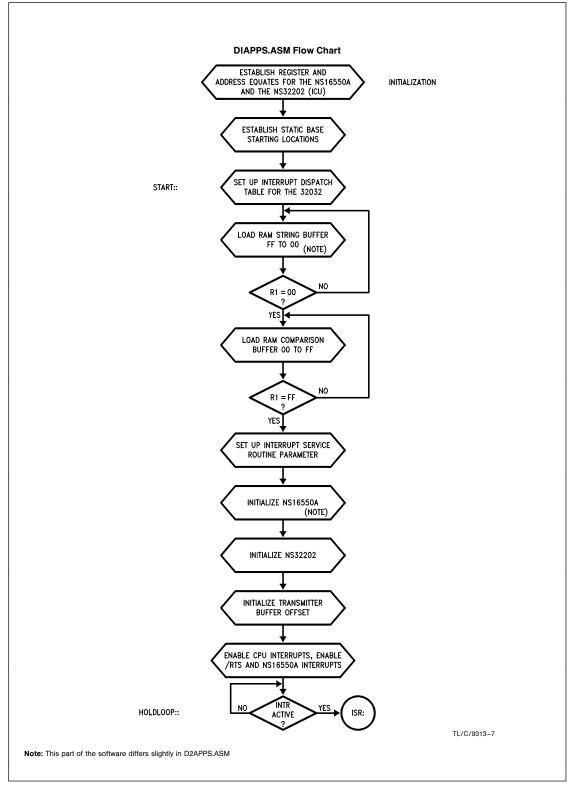

The following section describes the hardware and software for a fully asynchronous two board application. The two boards communicate simultaneously with each other via the NS16550As. Predetermined data is exchanged between the NS16550As and checked by the software for accuracy. Any data mismatches are flagged and stop the programs. Any data errors (i.e. overrun, parity, framing or break) will also stop the program. The NS16550A interface schematic, software flow chart and software are provided.

#### HARDWARE REQUIREMENTS

Running this application requires two NS32032-based boards. Each board must have one CPU, one ICU (NS32202), 256k of RAM (000000-03FFFF), the capability of running a monitor program (MON 32) and the capability of interfacing with a terminal. If MON 32 is not available, the display monitor service calls (SVC) must be altered to interface properly to the available terminal driver routines. In addition to these requirements, the NS16550A is enabled starting at address 0d00000.

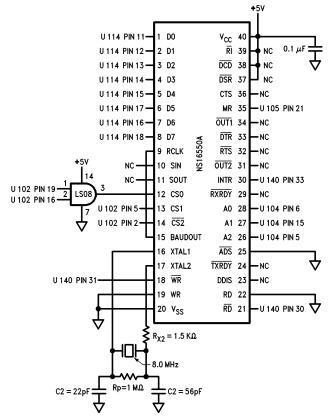

The system described above was implemented on two DB32032 boards and used as an alpha site to test the NS16550A during its development. An NS16550A and appropriate decode logic were wirewrapped to each board (see Figure 5 ). As shown, an 8 MHz crystal is used to drive the baud rate generator, but for baud rates at or below 56 kbaud a 1.8432 MHz crystal can be substituted with changes to the divisor. Once this hardware is on both boards 5 connections between the NS16550As must be made—SIN to SOUT, SOUT to SIN, CTS to RTS, RTS to CTS, and GND to GND. Each DB32032 board has a port for attaching a terminal and a port available for downloading code. The applications software for these boards is downloaded from a VAX™ running the GNX™ debugger (V1.02). Once the downloads are complete to both boards the program D1APPS.EXE is started, then D2APPS.EXE is started.

If a VAX or the GNX debugger is not available the code can be loaded into PROMs and run directly.

FIGURE 5. NS16550A and DB32032 Board Interconnections

TL/C/9313-5

#### **SOFTWARE OVERVIEW**

The programs shown at the end of this application note are the assembly listings for D1APPS.ASM and D2APPS.ASM. These can be assembled, linked and loaded to form the executable (.EXE) files. The flowchart shown before them illustrates both programs.

Both programs are interrupt driven. D1APPS.EXE has its transmitter empty interrupt disabled until it receives its first 16 bytes from D2APPS.EXE. This allows the two programs to be started at different times. Data flow is controlled between the programs via RTS and CTS handshakes. D1APPS.EXE is started first and it loops until the first data from D2APPS.EXE arrives. As D1APPS.EXE exits its receiver interrupt routine, it enables its transmitter interrupt and begins to send bytes to D2APPS.EXE.

Transmission of a block of 16 bytes occurs when the Tx FIFO of the NS16550A is empty, the Tx interrupt is enabled and the receiver activates its clear to send (CTS) signal. Each transmitter sends the next sequential block of data from a 256 byte buffer. When the bottom of the buffer is reached, the transmitter starts at the top of the buffer, again. The data transmitted from D1APPS.EXE to D2APPS.EXE is 00 to FF and from D2APPS.EXE to D1APPS.EXE is FF to 00. Since these are bench test programs for the NS16550A, the receiver subroutines compare the data they receive with the data they expect. This is done on a block-by-block basis and any mismatches result in both a message sent to the terminal and the program stopping.

## **DETAILED SOFTWARE DESCRIPTION**

Initialization begins by equating NS16550A and ICU (NS32202) registers to the addresses in memory. The equates finish with a list of offsets associated with the static base register. These offsets give the starting locations for the RAM areas assigned to be data buffers. These include the UART interrupt entry offset (irl\_mod); the string (sbuf), receive (rbuf), compare (cbuf) buffers and the interrupt table offset (intable).

At the code start (START::) the processor is put in the supervisor mode so that the interrupt dispatch table can be transferred from ROM to RAM. This transfer is essential in order to change the starting address of the UART interrupt service routine. To do this the interrupt service routine offset from the code start is calculated (isr-start). Combining this with the module table address (set-up by the linker, i.e., 9020) results in the interrupt table descriptor entry for UART interrupt service routine (isrent).

The next two sections of code load the data to be transmitted and compared into the RAM buffers sbuf and cbuf, respectively. The two programs differ at this point—D1APPS.EXE transmits 00 to FF and compares FF to 00 sequentially. D2APPS.EXE transmits FF to 00 and compares 00 to FF sequentially.

The NS16550A initialization starts with setting the divisor latch access bit, so the divisor can be loaded. It then determines the serial data format and disables all UART interrupts. The NS16550A initialization finishes by enabling and resetting the FIFOs and programming the receiver interrupt level for 14 bytes.

Next the ICU interrupt registers are set-up and interrupts are enabled. In program D1APPS.ASM the initialization finishes by enabling the receive data and line status interrupts. Since the transmitter FIFO empty interrupt is disabled D1APPS.EXE will stay in its hold loop until it receives data from D2APPS.EXE. D2APPS.EXE has its transmitter FIFO empty interrupt enabled at the end of its initialization, so it will send one block of 16 characters to D1APPS.EXE immediately.

When there are no interrupts pending and no service routines being executed, the programs run in a holding loop until the next interrupt.

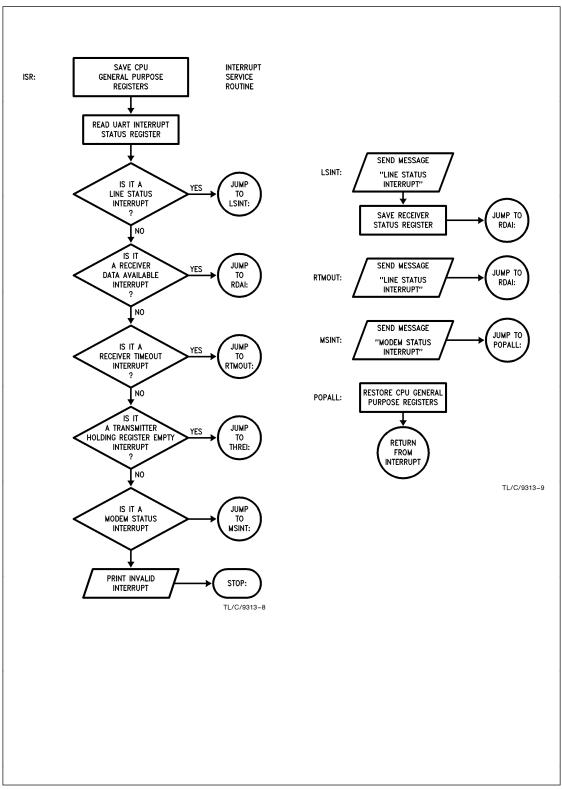

Whenever the CPU enters the service routine (isr:) it checks the interrupts identification register (IIR) for the type of interrupt pending and branches to the appropriate subroutine. If the IIR value doesn't match a known interrupt condition, an invalid interrupt message is sent to the terminal and the program stops. Out of the five possible interrupts, two (line status and receiver timeout) have simple routines that only send a message to the terminal and then branch to the receiver data available routine. Modem status interrupts send a message to the CRT and then stop the program. Two robust interrupt service routines exist—one for the receiver and one for the transmitter.

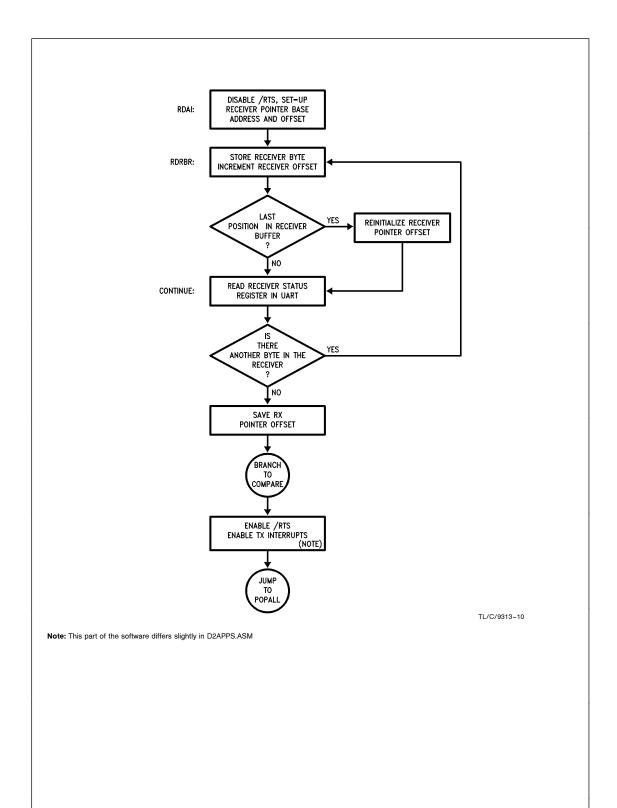

The receiver interrupt service routine (rdai:) does the following:

- Disables the RTS signal which stops the transmitter on the other board from sending more data.

- Transfers all data from the UART Rx FIFO to the RAM receiver buffer (rbuf).

- Branches to the compare subroutine when all data is transferred from the Rx FIFO.

- 4. Enables Tx interrupts in D1APPS.EXE.

- Enables the RTS signal which allows the transmitter on the other board to send another block of data.

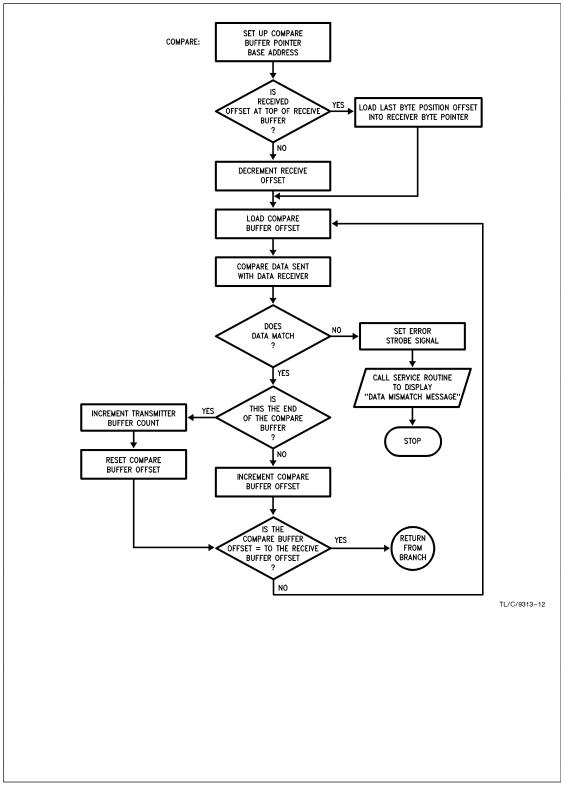

The compare interrupt service routine (compare:) does the following:

- Aligns the receive buffer pointer to the last character taken in to the receive buffer (rbuf).

- Compares each new byte in rbuf with the expected value (data stored in cbuf).

- Sends a data mismatch message to the terminal and stops the program if the rbuf data fails to match the cbuf data

- Returns to rdai: when all of the new data in rbuf has compared successfully.

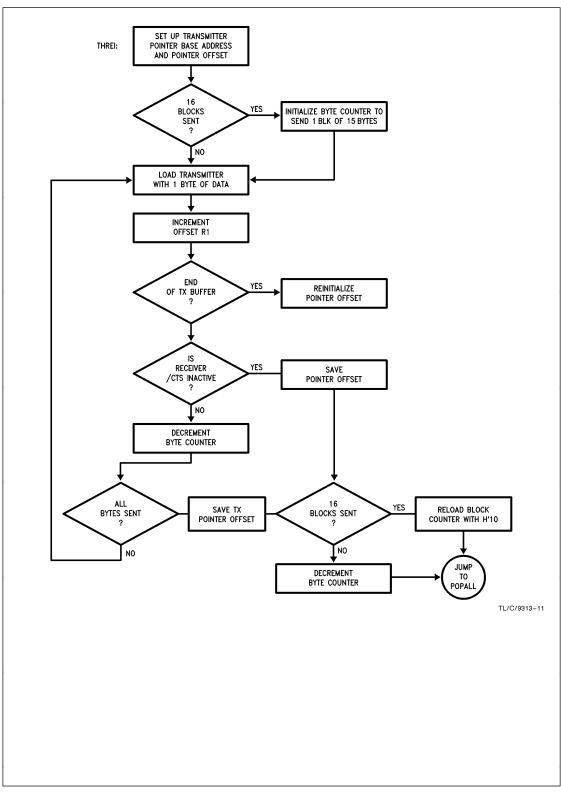

The transmitter interrupt service routine (threi:) does the following:

- Decides whether to send 16 or 15 bytes in a block of data. Note: This decision is for testing purposes.

- 2. Sends one byte of data.

- Checks for an active CTS condition. If it is active then it sends another byte of data. It continues to check and send a byte of data until all 15 or 16 bytes are sent.

```

#THIS PROGRAM RUNS USING 2 DB32000 BOARDS WITH 16550AB ENABLED AT ADDRESS 0d00000

#WIRE-WRAPPED ON THE BOARDS. THIS SOFTWARE TRANSMITS THE DATA OO THROUGH FF #REPEATEDLY TO THE REMOTE UART AND EXPECTS TO REPEATEDLY RECEIVE THE DATA FF

#THROUGH OO FROM THE REMOTE UART. IT SHOULD BE RUN IN CONJUNCTION WITH THE

#PROGRAM D2APPSC.ASM RUNNING ON THE OTHER DB32000 BOARD. THE TX PIN OF

#THIS 16550A SHOULD CONNECT TO THE RX PIN OF THE 16550A ON THE OTHER BOARD AND

#VICE VERSA. ALSO, THE CTS PIN OF THIS 16550A SHOULD BE CONNECTED TO THE RTS PIN

#OF THE 16550A ON THE OTHER BOARD AND VICE VERSA. THIS WILL ENABLE THE

# APPROPRIATE HANDSHAKES TO OCCUR.

#TO RUN THIS PROGRAM YOU MUST:

1. CONNECT THE RX & TX OF THE 2 16550As ON THE 2 DB32000 BOARDS 2. CONNECT THE CTS & RTS OF THE 2 16550As ON THE 2 DB32000 BOARDS

3. DOWNLOAD DIAPPS.EXE TO THIS BOARD VIA THE GNX DEBUGGER [REV 1.02]

4. DOWNLOAD D2APPS.EXE TO OTHER BOARD VIA THE GNX DEBUGGER [REV 1.02]

5. START D1APPS.EXE RUNNING ON THIS DB32000 BOARD6. START D2APPS.EXE RUNNING ON THE OTHER DB32000 BOARD

#PROGRAM DETAILS:

# ISR contains the TX SERVICE ROUTINE

# TX OVERWRITES are PREVENTED by the ICU

# TX FIFO is CLEARED before a transmission

# DATA SENT OO ----- FF

# DATA RECEIVED and COMPARED FF ----- 00

# BAUDRATE 128k WITH A 8.0 MHZ XTAL INPUT TO THE 16550A

#******************** ESTABLISH 16550A REGISTER ADDRESSES ***************

.globi

.set rxd,

0x0d00000

#Equate registers to their addresses

.set txd,

0x0d00000

.set ier,

0x0d00004

0x0d00008

.set iir,

0x0d00008

.set fcr,

.set lcr,

0x0d0000c

0x0d00010

.set mcr.

.set lsr,

0x0d00014

.set msreg,

0x0d00018

.set scr,

0x0d0001c

#*********** ESTABLISH ADDRESSES FOR THE 32202 (ICU) ********************

.set a0,4

#Establish address alignment

#between CPU and ICU

#ICU register addresses

.set icu hvct,0

.set icu_svct,1 *a0

.set icu_svct,1 *a0

.set icu_elgt,2 *a0

.set icu_tpl,4 *a0

.set icu_ipnd,6 *a0

.set icu_isrv,8 *a0

TI /C/9313-13

```

```

.set icu_imsk,10 *a0

.set icu csrc,12 *a0

.set icu fprt,14 *a0

.set icu mct1,16 *a0

.set icu ciptr,18 *a0

.set icu_pdat,19 *a0

.set icu ips,20

.set icu_pdir,21 *a0

.set icu_cctl,22 *a0

.set icu_cict1,23 *a0

#First ICU register address

.set icu_addr,0xfffe00

#**************************** STATIC BASE STARTING LOCATIONS *******************

.set 1rl mod, 17*4

.set irl off, 17*4+2

.set start2, 0x0

#The following are static base variables

.set startl, 0x0a

#used as base pointers. Start1/2 = flags

.set txflag, 0x14

#txflaf = flag, sbuf = area used to

.set sbuf, Oxle

#store data to be transmitted, rbuf =

.set rbuf, 0x4ie

.set cbuf, 0x6le

#area used to store received data,

#cbuf = area used to store compare

.set intable, 0x8le

#buffer, intable = base pointer to the

#interrupt table

#******************* SET UP DISPATCH TABLE FOR THE 32032 ****************

bicpsrw $(0x100)

#Clear intr's

movd $0x0c,r0

#Set for monitor svc to move intbase

movd $0x05555555,rl

#from ROM to ram because you have

addr intable(sb),r2

#to change the address for the

movd SOxOc,r3

#interrupt service routine.

svc

#Actual svc for move

sprd intbase, r2

#Put base addr of intbase in r2

movd isrent,irl_mod(r2) #Put offset of isr into 1st location

#of dispatch table

#****************** LOAD TRANSMITTER BUFFER (OO to FF) *******************

addr sbuf(sb),r0

movd $0,r1

senddat:

#RO contains string buffer ptr.

#R1 contains offset

movb $0,r2

#Init data reg.

sbufloop:

movb r2,0(r0)[r1:b]

#Load char. to string buffer

addqw 1,rl

#Increment offset ptr.

addqw 1,r2

#Increment data

cmpw rl,$256

#Check for 256 chars. loaded

bne

sbufloop

#Jump back if not done

addr cbuf(sb),r0

#RO contains pointer

compdat:

movd

$0,r1

#Rl contains offset

$0x0ff,r2

dvom

#Init data reg.

cbufloop:

movb r2,0(r0)[r1:b]

#Load char. to compare buffer

addqw l,rl

#Increment ptr. offset

subb $1,r2

cmpw r1,$256

#Decrement data

#Check for 256 chars. loaded

TI /C/9313-14

```

```

#Jump back if not done

bne

cbufloop

movd $0x0ff,start2(sb)

#Initialize compare

movd $0x0ff,start1(sb)

#Initialize receiver data intr

movd $16,blk16cnt

#Initialize 16 byte block counter

movd $0,sbufcnt

#Initialize string bufffer transmitted

#count

#**************************** 16550A INITIALIZATION ***************************

#Set dlab = 1 for divisor latch access

#Low divisor latch 128k w/8.0 MHz xtal

$0x080.1cr

movb

S4,txd

movb

SO.ier

#Upper divisor latch

movb

#Dlab = 0, 8 bits, no parity, 1 stop

$0x003,1cr

dvom

#Disable UART interrupts

movb $0,1er

movb $0x0c7,fcr

#Fifo=> trigger = 14, reset & enable

movd

$icu addr,r0

#RO = icu address

movb

$0xca,icu_mctl(r0)

#Set mode : 8 bit bus mode,

freeze counters,

disable interrupts,

fixed priority.

movqb 0,icu cctl(r0)

#Halt the counters

movqb -1,icu ips(r0)

#Set all pins to interrupt source

movqb 0,icu_carc(r0)

#No cascaded interrupts (low reg)

movqb 0,icu csrc+a0(r0)

# (high reg)

movb $0x10, Icu_svct(r0)

#Set interrupt base vector

movqb -1,icu_e\overline{1}gt(r0)

#Set level triggering mode (low reg)

movqb -1,icu_elgt+a0(r0)

#(high reg)

movqb $2,icu_tpl(r0)

#Set level triggering mode (low reg)

movqb 0,icu_tpl+a0(r0)

#(high reg)

#Set highest priority to 0 (low reg)

movqb 0,icu_fprt(r0)

movqb 0,icu_fprt+a0

#(high reg)

#Clear intr in-service regs (low reg)

movqb 0,icu_isrv(r0)

movqb 0,icu_isrv+a0(r0)

movqb -1,icu_imsk(r0)

#(high reg)

#Mask all intr (low reg)

movqb -1,icu imsk+a0(r0)

#(high reg)H

setcfg [i]

#Enable vectored intrp (I=1)

movd $icu_addr,r0

movb $0x0\overline{2}, icu mctl(r0)

#Fixed mode, 8 bit bus mode

movb $0x010,icu cct1(r0)

#Set to internal sampling

movb $0xfd,icu_imsk(r0)

#Enable irl

movb $0xft,icu imsk+a0(r0)

#Mask all other interrupts

bispsrw \$(0x80\overline{0})

#Enable cpu intr's

movd SO.rl

#Initialize transmitter buffer offset

#************************** ENABLE 16550A INTERRUPTS ********************

movb $2,mcr

#Clear outl, out2 and enable rts

movb $0x05,ier

#Enable all but modem status interrupts

#and the THRE so the boards can be

#started.

#************************ ENDLESS LOOP WAITING FOR INTERRUPTS ******************

TL/C/9313-15

```

```

holdloop:

nop

br holdloop

isr:

save [r0,r1,r2,r3,r4,r5,r6,r7]

movb lir,r0

#RO- contains iir

cmpb r0,$0x0c6

beq lsint

#Line status interrupt

cmpb r0,$0x0c4

beq rdai

#Receiver interrupt

cmpb r0,$0x0cc

bea rtmout

#Rec timeout interrupt

cmpb r0,$0x0c2

beg threi

#THRE interrupt

cmpb r0,$0x0c0

beg msint

#Modem status interrupt

save [r0,r1,r2,r3]

movd $4,r0

addr message2,rl

movd $21,r2

movd $0,r3

SVC

restore [r0,r1,r2,r3]

jump stop

#Restore all registers

#********************* RECEIVER TIMEOUT INTERRUPT ROUTINE *********************

rtmout:

jump rdai

#This portion of the program is reached by a positive test for the received data #available interrupt. Once in this routine each byte is removed from the FIFO, #placed in a designated static base memory location and the LSR is tested to see #if the data ready (DR) bit is still set. Data is removed from the FIFO and #placed in memory until the DR bit is no longer set. The data sent will be

#compared to known data, located in another designated static base location, by

#calling the compare subroutine.

rdai:

movb $0, mcr

#Disable RTS; stop transmission

addr rbuf(sb),r4

#r4 contains rbuf base address

movd rbufoff,r6

#Put rbuf offset runner into r6

rdrbr:

movb rxd, 0(r4)[r6:b]

#Store a byte in the receiver buffer

cmpb $0x00,0(r4)[r6:b]

#Is it the last character

addqw 1,r6

#Increment offset ptr.

addqw 1,rbufoff

#Track r6

bne continue

movw $0,r6

#Reset pointer offset

movw $0,rbufoff

#Reset rbufoff

continue:

movb lsr,r3

#Read lsr

andb $01,r3

#Mask all but bit 0

cmpb $01,r3

TL/C/9313-16

```

```

#Read rbr again if set

bea rdrbr

#Put result of r6 back into rbufoff

movd r6, rbufoff

bsr compare

movb $7,ier

#Turn on transmitter interrupts

movb $2,mcr

#Enable rts

jump popall

#Before the transmitter sends data, the data has been loaded into static base

#memory for transmission. The transmitter routine is called to send data. (ie

#THREI is set) Data is sent as 16 blocks of 16 bytes and 1 block of 15 bytes

#continuously. NOTE: Before transmission occurs /CTS is checked to ensure that

#the receiver is ready.

#RO contains base pointer

thre1:

addr sbuf(sb),r0

movw xmitoff,rl

#setup xmit ptr offset

cmpd $0,blk16cnt

#Check to see if it is the 16th block *

beg send15

#Yes, send only 15 bytes instead of 16 *

#No, send 16 bytes *

movd $0x10,r7

jump sendnext

#Jump around 15 byte load *

sendl5:

movd $0x0f,r7

#Load counter for 15 byte load *

sendnext:

movb O(r0)[r1:b],txd

#Load a byte into the transmitter

addqw l,rl

cmpw rl,$256

#Are we one address past end of table

beq reload

#Yes, reload ptr

finish:

save [r7]

movb msreg,r7

#Read modem status reg

#Mask all bits except CTS (MSR4)

andb $0x10,r7

cmpb $0,r7

#Check for disabled CTS

restore [r7]

#Wait for active CTS (MSR4=1)

beq abort

subb $1,r7

cmpb $0,r7

#No, decrement counter and continue

#Is byte counter 0?

bne sendnext

#No, send next byte

abort:

movw rl,xmitoff

\# save \ xmit \ ptr \ offset \ in \ ram

cmpd $0,blkl6cnt

#Check to see if it is l6th block *

beq setsndl6

#Yes, reload block counter *

#Decrement block counter *

subb $1,blk16cnt

#Finished sending 16 bytes

jump popall

movd $16,blk16cnt

setsnd16:

#Reload block counter

#Finished sending 15 bytes *

jump popali

movd $0,rl

reload:

#Reset offset

jump finish

#Go back and finish

#************************* LINE STATUS INTERRUPT ROUTINE ***********************

lsint:

save [r0,r1,r2,r3]

movd $4,r0

addr message6,rl

movd $25, r2

movd SO,r3

SVC

restore [r0,r1,r2,r3]

movb lsr,r3

#Read lsr

jump rdai

#*********************** MODEM STATUS INTERRUPT ROUTINE ***********************

TL/C/9313-17

```

```

msint:

save [r0,r1,r2,r3]

movd $4,r0

addr message7,rl

movd $26, r2

movd $0,r3

avc

movb 0x0d00018,r0

restore [r0,r1,r2,r3]

#This subroutine is called by the receiver interrupt routine which has set the

#receiver offset (rbufoff) to point at the last byte received. This subroutine

#uses the compare offset (compoff) pointer as the pointer for both receive

#buffer data and compare buffer data. Each location is compared to ensure data #sent is identical to data received. This is done until compoff equals roufoff

#stopping the process and returning from the interrupt. NOTE: Data being

#received is known data and an exact copy is loaded into memory prior to any

#transmission.

compare:

addr cbuf(sb),rl

cmpd $0,r6

#R1- base address of cbuf base

#Check for potential invalid subtraction

beg zeror6

#Jump around subtraction

subd $1,r6

#Jump around subtraction fix

jump compbyte

zeror6:

movd $0xff,r6

compbyte:

movd compoff, r5

cmpb 0(r1)[r5:b], 0(r4)[r5:b] #Compare data sent to data received

bne wrong

#Branch and set outl if wrong

cmpb $0x00,0(r4)[r5:b] #Check for end of buffer

#Branch and increment pointers

bne notend

jump reloadl

#Test for having compared all bytes

notend:

addd $1,compoff

#Increment pointer

notend1:

cmpd r5,r6

beg bye

jump compbyte

reload1:

addd $1,sbufcnt

#Increment transmiter cnt

movd $0,compoff

#Reload offset of pointer

jump notendl

wrong:

nop

movb $0x0c,mcr

#Set out 2, for error strobe

save [r0,r1,r2,r3]

#Save register for supervisor call

movd $4,r0

#Value required by svc call

addr message8,rl

#Mover address of message into rl

movd $17,r2

#Number of characters into r2

movd $0,r3

#Value required by svc call

svc

#Actual call

restore [r0,r1,r2,r3]

#Restore registers

stop:

nop

jump stop

#Test point

TL/C/9313-18

```

```

#3/30/87.....D2APPS.ASM.......ADAPTED ORIGINALLY FROM D1RON56K.ASM

#THIS PROGRAM RUNS USING 2 DB32000 BOARDS WITH 16550As ENABLED AT ADDRESS

#0d00000 WIRE-WRAPPED ON THE BOARDS. THIS SOFTWARE TRANSMITS THE DATA FF

#THROUGH OO REPEATEDLY TO THE REMOTE UART AND EXPECTS TO REPEATEDLY RECEIVE

#THE DATA OO THROUGH FF FROM THE REMOTE UART. IT SHOULD BE RUN IN CONJUNCTION

#WITH THE PROGRAM DIAPPS.ASM RUNNING ON THE OTHER DB32000 BOARD. THE TX PIN OF

#THIS 16550A SHOULD CONNECT TO THE RX PIN OF THE 16550A ON THE OTHER BOARD AND

#VICE VERSA. ALSO, THE CTS PIN OF THIS 16550A SHOULD BE CONNECTED TO THE RTS PIN #OF THE 16550A ON THE OTHER BOARD AND VICE VERSA. THIS WILL ENABLE THE

# APPROPRIATE HANDSHAKES TO OCCUR.

#TO RUN THIS PROGRAM YOU MUST:

1. CONNECT THE RX & TX OF THE 2 16550As ON THE 2 DB32000 BOARDS 2. CONNECT THE CTS & RTS OF THE 2 16550As ON THE 2 DB32000 BOARDS

3. DOWNLOAD D2APPS.EXE TO THIS BOARD VIA THE GNX DEBUGGER [REV 1.02]

4. DOWNLOAD DIAPPS.EXE TO OTHER BOARD VIA THE GNX DEBUGGER [REV 1.02]

5. START DIAPPS.EXE RUNNING ON THE OTHER DB32000 BOARD

6. START D2APPS.EXE RUNNING ON THIS DB32000 BOARD

#PROGRAM DETAILS:

# ISR contains the TX SERVICE ROUTINE

# TX FIFO is CLEARED before a transmission

# DATA SENT FF ---- 00

# DATA RECEIVED and COMPARED OO ----- FF

# BAUDRATE 128k WITH A 8.0 MHZ XTAL INPUT TO THE 16550A

#************************* ESTABLISH 16550A REGISTER ADDRESSES *****************

.qlobl

ısr

.set rxd,

0x0d00000

#Equate registers to their addresses

0x0d00000

.set txd,

0x0d00004

.set ier.

0x0d00008

.set iir,

0x0d00008

.set fcr.

.set lcr,

0x0d0000c

.set mcr,

0x0d00010

0x0d00014

.set lsr,

.set msreg,

0x0d00018

.set scr,

0x0q0001c

#************** ESTABLISH ADDRESSES FOR THE 32202 (ICU) *****************

.set a0,4

#Establish address alignment

#between CPU and ICU

#ICU register addresses

.set icu hvct,0

.set icu_svct,1 *a0

.set icu_elgt,2 *a0

.set icu_tpl,4 *a0

.set icu ipnd,6 *a0

.set icu_isrv,8 *a0

.set icu_imsk,10 *a0

.set icu csrc,12 *a0

TL/C/9313-20

```

```

.set icu_fprt,14 *a0

.set icu mctl,16 *a0

.set icu ciptr,18 *a0

.set icu_pdat,19

*a0

*a0

.set icu ips,20

.set icu_pdir,21 *a0

.set icu_cct1,22 *a0

*a0

.set icu_cict1,23 *a0

#First ICU register address

.set icu addr, 0xfffe00

.set irl_mod, 17*4

#Dispatch table offset for IR1 entry

.set sbuf, Oxle

.set rbuf, Ox4le

#sbuf = area used to

#store data to be transmitted, rbuf =

.set cbuf, 0x6le

#area used to store received data,

.set intable, 0x8le

#cbuf = area used to store compare

#buffer, intable = base pointer to the

#interrupt table

#****************** SET UP DISPATCH TABLE FOR THE 32032 *****************

start::

bicpsrw $(0x100)

#Clear intr's

#Set for monitor svc to move intbase

movd $0x0c,r0

#from ROM to ram because you have

#to change the address for the

movd $0x05555555,rl

addr intable(sb),r2

#interrupt service routine.

movd $0x0c,r3

#Actual svc for move

SVC

sprd intbase, r2

#Put base addr of intbase in r2

movd isrent, irl_mod(r2) #Put offset of isr into lst location

#of dispatch table

#******************* LOAD TRANSMITTER BUFFER (FF to 00) ******************

senddat:

addr sbuf(sb),r0

\#RO contains string buffer ptr.

movd $0,rl

#Rl contains offset

movb S0x0ff.r2

#Init data reg.

#Load char. to string buffer

sbufloop:

movb r2,0(r0)[r1:b]

#Increment offset ptr.

addgw 1,rl

#Increment data

#Check for 256 chars. loaded

subb $1,r2

cmpw r1,$256

bne

sbufloop

#Jump back if not done

#****************** LOAD COMPARISON BUFFER (OO TO FF) ******************

addr cbuf(sb),r0

movd $0,r1

#RO contains pointer

compdat:

#Rl contains offset

movb $0, r2

#Init data reg.

movb r2,0(r0)[r1:b]

cbufloop:

#Load char. to compare buffer

addgw l.rl

#Increment ptr. offset

addqw 1,r2

#Decrement data

#Check for 256 chars. loaded

cmpw r1,$256

bne

cbufloop

#Jump back if not done

#********** SET UP INTERRUPT SERVICE ROUTINE PARAMETERS *****************

movd $16,blk16cnt

#Initialize 16 byte block counter

TL/C/9313-21

```

```

#************************ 16550A INITIALIZATION ********************

movb $0x080,1cr

#Set dlab = 1 for divisor latch access

#Low divisor latch 56k w/8.0 xtal

dvom

$4,txd

$0,1er

dvom

#Upper divisor latch

movb

$0x003,1cr

#Dlab = 0, 8 bits, no parity, 1 stop

movb

$0,ier

#Disable UART interrupts

movb $0x0c7,fcr

#Fifo=> trigger = 14, reset & enable

#RO = icu address

movd

$icu_addr,r0

#Set mode : 8 bit bus mode,

$0xca,icu_mctl(r0)

movb

freeze counters,

disable interrupts,

fixed priority.

movqb 0,icu cctl(r0)

#Halt the counters

movqb -1,icu_ips(r0)

#Set all pins to interrupt source

movqb 0,1cu csrc(r0)

#No cascaded interrupts (low reg)

movqb 0,1cu_csrc+a0(r0)

# (high reg)

movb $0x10, icu svct(r0)

#Set interrupt base vector

movqb -1,icu_elgt(r0)

#Set level triggering (low reg)

movqb -1,icu_elgt+aO(r0)

movqb 92,icu_tpl(r0)

movqb 0,icu_tpl+aO(r0)

movqb 0,icu_fprt(r0)

#(high reg)

#Set high polarity mode (low reg)

#(high reg)

#Set highest priority to 0 (low reg)

movqb 0,1cu fprt+a0

#(high reg)

movqb 0,icu_isrv(r0)

#Clear intr in-service regs (low reg)

movqb 0,icu isrv+a0(r0)

#(high reg)

movqb -1,icu_imsk(r0)

#Mask all intr (low reg)

movqb -1,icu imsk+a0(r0)

#(high reg)H

setcfg [i]

#Enable vectored intrp (I=1)

movd $icu_addr,r0

movb $0x02,icu_mctl(r0)

#Fixed mode, 8 bit bus mode

movb $0x010,icu_cctl(r0)

#Set to internal sampling

movb $0xfd,icu_imsk(r0)

movb $0xff,lcu_imsk+a0(r0)

#Enable irl

#Mask all other interrupts

bispsrw \$(0x80\overline{0})

#Enable cpu intr's

movb $2,mcr

#Clear out1, out2 and enable rts

endinit:

movb $0x07,1er

#Enable all but modem status interrupts

#****************** ENDLESS LOOP WAITING FOR INTERRUPTS *****************

holdloop:

nop

br holdloop

save [r0,r1,r2,r3,r4,r5,r6,r7]

isr:

movb iir,r0

#RO- contains iir

cmpb r0,$0x0c6

beq lsint

#Line status interrupt

cmpb r0,$0x0c4

beg rdai

#Receiver interrupt

cmpb r0,$0x0cc

TL/C/9313-22

```

```

bea rtmout

#Rec timeout interrupt

cmpb r0,$0x0c2

beq threi

#THRE interrupt

cmpb r0,$0x0c0

beq maint

#Modem status interrupt

save [r0,r1,r2,r3]

movd $4,r0

addr message2,rl

movd $21,r2

movd $0,r3

svc

restore [r0,r1,r2,r3]

#Restore all registers

jump stop

#******************** RECEIVER TIMEOUT INTERRUPT ROUTINE ***********************

rtmout:

jump rdai

#This portion of the program is reached when the received data available #interrupt is active. Once in this routine each byte removed from the FIFO

#is placed in the designated static base memory location (labelled rbuf).

#The data ready bit (DR) in the LSR is checked before each byte is removed

#from the FIFO. Data sent will be compared to known data in another designated

#static base area (labelled cbuf) by calling the compare subroutine.

movb $0,mcr

rdai:

#Disable RTS; stop transmission

addr rbuf(sb),r4

#r4 contains rbuf base address

movd rbufoff,r6

#Put rbuf offset runner into r6

rdrbr:

movb rxd,O(r4)[r6:b] #Store a byte in the receive buffer cmpb $0xff,O(r4)[r6:b] #Is it the last character addqw 1,r6 #Increment offset ptr.

movb rxd,0(r4)[r6:b]

addqw 1,rbufoff

#Track r6

bne continue

movw $0,r6

#Reset pointer offset

movw $0,rbufoff

#Reset roufoff

continue:

movb lsr,r3

#Read lsr

andb $01,r3

#Mask all but bit 0

cmpb $01,r3

beq rdrbr

#Read rbr again if set

movd r6,rbufoff

#Put result of r6 back into rbufoff

bsr compare

movb $2,mcr

#Enable rts

jump popall

#The transmitter sends data previously loaded into the static base memory area

#labelled sbuf. Thids routine sends data as 16 blocks of 16 bytes and 1 block

#of 15 bytes, continuously. NOTE: Before each block transmission occurs /CTS

#1s checked to ensure that the receiver ready.

TL/C/9313-23

```

```

threi:

addr sbuf(sb),r0

#RO contains base pointer

movw xmitoff,rl

#setup xmit ptr offset

#Check to see if it is the l6th block

cmpd $0,blk16cnt

beg sendl5

\# Yes, send only 15 bytes instead of 16

movd $0x10,r7

#No, send 16 bytes

#Jump around 15 byte load

#Load counter for 15 byte load

jump sendnext

send15:

movd $0x0f,r7

sendnext:

movb 0(r0)[r1:b],txd

#Load a byte into the transmitter

addqw l,rl

cmpw rl,$256

#Are we one address past end of table

#Yes, reload ptr

beg reload

finish:

save [r7]

#Read modem status reg

#Mask all bits except CTS (MSR4)

movb mareg,r7

andb $0x10,r7

cmpb $0,r7

#Check for disabled CTS

restore [r7]

beg abort

#Leave on inactive CTS (MSR4=0)

#No, decrement counter and continue

subb $1,r7

cmpb $0,r7

#Is byte counter 0?

bne sendnext

#No, send next byte

abort:

movw rl,xmitoff

#save xmit ptr offset in ram

cmpd $0,blkl6cnt

#Check to see if it is 16th block

beg setsndl6

#Yes, reload block counter

subb $1,blkl6cnt

#Decrement block counter

jump popall

#Finished sending 16 bytes

setsnd16:

movd $16,blkl6cnt

#Reload block counter #Finished sending 15 bytes

jump popall

movd $0,rl

#Reset offset

reload:

#Go back and finish

jump finish

lsint:

save [r0,r1,r2,r3]

movd $4,r0

addr message6,rl

movd $25,r2

movd $0,r3

SVC

restore [r0,r1,r2,r3]

movb lsr,r3

#Read lsr

jump rdai

#************************* MODEM STATUS INTERRUPT ROUTINE *********************

save [r0,r1,r2,r3]

movd $4,r0

addr message7,rl

movd $26, r2

movd $0,r3

SVC

movb 0x0d00018,r0

restore [r0,r1,r2,r3]

#The receiver subroutine branches to this subroutine after it has removed all of

#the data from the Rx FIFO. The receive offset (rbufoff) is changed to point to

#the last byte received in rbuf. The compare offset (compoff) points to each

#byte in the receive buffer and its associated byte in the compare register.

#Compoff is incremented after each successful comparison and the comparisons

TL/C/9313-24

```

```

#end when compoff equals rbufoff. NOTE: Data being received by this test program

#is known data and a copy of it is loaded into cbuf before transmissions begin.

addr cbuf(sb),rl

#R1- base address of cbuf base

cmpd $0,r6

#Check for potential invalid subtraction

beq zeror6

#Jump around subtraction

subd $1,r6

jump\ compbyte

#Jump around subtraction fix

zeror6:

movd $0xff,r6

compbyte:

movd compoff, r5

cmpb O(r1)[r5:b], O(r4)[r5:b] #Compare data sent to data received

#Branch and set outl if wrong

bne wrong

cmpb $0xff,0(r4)[r5:b] #Check for end of buffer

#Branch and increment pointers

bne notend

jump reloadl

#Test for having compared all bytes

notend:

addd $1,compoff

#Increment pointer

notendl:

cmpd r5,r6

beq bye

jump compbyte

reloadl:

addd Sl.sbufcnt

#Increment transmiter ont

movd $0,compoff

#Reload offset of pointer

jump notendl

#Set out 2, for error strobe

wrong:

movb $0x0c,mcr

#Save register for supervisor call

save [r0,r1,r2,r3]

movd $4,r0

#Value required by svc call

addr message8,rl

#Mover address of message into rl

#Number of characters into r2

movd $17,r2

#Value required by svc call #Actual call

movd SO,r3

svc

restore [r0,r1,r2,r3]

#Restore registers

stop:

nop

jump stop

#Test point

bye:

ret 0

restore [r0,r1,r2,r3,r4,r5,r6,r7]

popall:

reti

messagel: .byte 13,10, "Compare Complete",13,10

message2: .byte 13,10, "Invalid Interrupt",13,10 message3: .byte 13,10, "Receiver Timeout",13,10

message4: .byte 13,10, "Receive Timeout",13,10

message4: .byte 13,10, "Receive data available Interrupt",13,10

message5: .byte 13,10, "THRE Interrupt",13,10

message6: .byte 13,10, "Line Status Interrupt",13,10

message7: .byte 13,10, "Modem Status Interrupt",13,10

message8: .byte 13,10, "Data Mismatch",13,10

TL/C/9313-25

```

xmitoff: .double 0

compoff: .double 0

blk16cnt: .double 0

sbufcnt: .double 0

rbufoff: .double 0

isrent: .word 0x9020

isr-start .word

#Mod table

#Offset of service routine for #Dispatch table.

TL/C/9313-26

Lit. # 100491

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor**

National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

**National Semiconductor** Europe

Fax: (+49) 0-180-530 85 86 Fax: (+49) 0-180-530 85 86 Email: cnjwge@tevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 **National Semiconductor** Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd.

Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408