Edited by Bill Travis and Anne Watson Swager

#### **Circuit detects first event**

Kelly Flaherty, National Semiconductor, San Mateo, CA

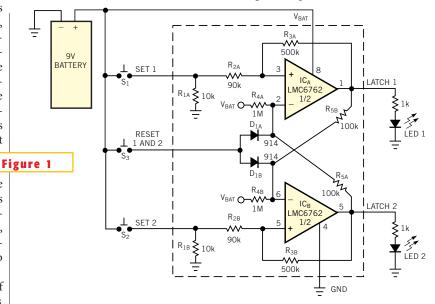

HE CIRCUIT IN Figure 1 is a "firstevent" indicator, like a game show's "who's first to answer" detector. It indicates which of the two momentary switches, S<sub>1</sub> or S<sub>2</sub>, closes first by latching the corresponding channel,  $IC_A$  or  $IC_B$ , to a high state. As either of the outputs latches high and lights its respective LED, it locks out the other channel and prevents it from triggering. The other momentary switch, S<sub>3</sub>, resets either of the latched outputs to its initial low (LEDoff) state. At the initial condition, the positive input of each comparator is approximately at 0V, because both outputs are low. The negative inputs are at  $V_{BAT}/11$ , as set by voltage divider  $R_4$ and R<sub>5</sub>. In this initial condition, assume that S<sub>1</sub> is momentarily closed. The positive input of IC<sub>A</sub> becomes <sup>5</sup>/<sub>6</sub>(V<sub>BAT</sub>), as set by voltage divider  $R_{2A}$  and  $R_{3A}^{DAI}$ . Because  $\frac{5}{6}(V_{BAT})$  is greater than VBAT/11, the output of  $IC_A$  goes high, and the positive input of IC<sub>A</sub> latches its threshold to approximately V<sub>BAT</sub>/6.

Correspondingly, the negative input of  $IC_B$  latches to approximately  $V_{BAT}$ , thus preventing  $S_2$  from triggering  $IC_B$ 's output high.  $S_3$  resets (turns off) either of the active outputs by pulling the inverting inputs one diode drop below  $V_{BAT}$ . Both channels are then in their initial condition and ready to go again. The LMC6762

| Circuit detects first event                           | 89 |

|-------------------------------------------------------|----|

| High-speed pulse generator<br>has programmable levels | 90 |

| Low-battery indicator<br>has high efficiency          | 92 |

| LCD-bias supply provides precise tracking             | 94 |

| Rolling-code generator uses flash $\mu$ C             | 94 |

| SEPIC generates 5V at 100 mA                          | 98 |

| Look-up table helps bit flipping                      | 98 |

|                                                       |    |

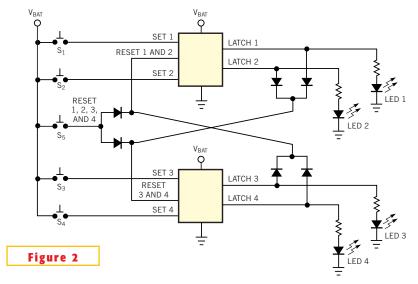

dual comparator is a good fit for this application, because it draws only  $7-\mu A$  quiescent current, and it has rail-to-rail inputs and outputs. The comparator's sourcing capability allows it to easily drive an LED. Figure 2 shows how you

ideas

can cascade two first-event detectors to obtain more channels.

Is this the best Design Idea in this issue? Vote at www.ednmag.com/edn mag/vote.asp.

With the addition of six diodes, you can cascade two first-event detectors.

# High-speed pulse generator has programmable levels

John Guy, Maxim Integrated Products, Sunnyvale, CA

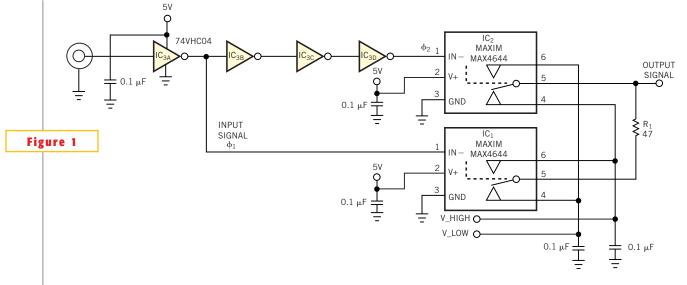

ILLIPUTIAN dimensions associated with the submicron geometries of most digital and many analog processes result in much faster circuit operation. As ICs speed up, the rise and fall times of most pulse and function generators, which are typically 5 nsec, become inadequate for measuring time intervals lower than 20 nsec. You can overcome this limitation with analog comparators or advanced CMOS logic gates, which create faster digital edges. Their rise and fall times are fast enough, but the signal levels include ground

and  $V_{\rm CC}$  only. Designers have applied the submicron processes that high-speed digital cir-

cuits use to analog switches as well, so the turn-on and turn-off times for these

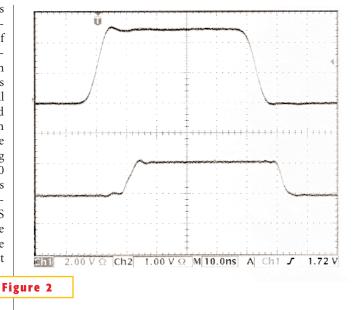

The input (lower) and output (upper) traces illustrate fast output transitions and settable output levels.

switches also produce fast rise and fall times. What's more, an SPDT (singlepole, double-throw) switch can create pulses whose high and low levels are programmable.

feature of analog А switches that hinders their use as pulse generators is the intrinsic built-in delay-the break-before-make timethat guarantees that an SPDT switch does not short the two switched terminals together during a transition. Unfortunately, this delay and the switches' finite turn-on time also extends the rise and fall times. You can avoid this effect by adding a dynamic pullup and a dynamic pulldown to the circuit (Figure 1). A sufficiently low pullup and pulldown impedance can drastically improve the cor-

responding rise and fall times. The input clock signal,  $\Phi_1$ , controls an

Analog switches provide dynamic pull-up and pull-down at the output of this pulse generator to ensure fast rise and fall times.

SPDT analog switch, IC<sub>1</sub>, which the circuit configures as the pullup/pulldown driver. The input clock signal also drives a high-speed CMOS inverter, IC<sub>3</sub>, to create a delayed clock signal,  $\Phi_2$ . The delayed clock drives an SPDT analog switch, IC<sub>2</sub>, which the circuit configures as the output driver.

Consider the steady-state condition in which  $\Phi_1$  is low and  $\Phi_2$  is high. IC<sub>1</sub>'s COM pin and IC<sub>2</sub>'s COM pin connect to V\_LOW, and a rising edge on  $\Phi_1$  causes IC<sub>1</sub> to pull the output signal high. Because the series resistor, R<sub>1</sub>, is large with respect to the MAX4644's on-resistance, or 47 $\Omega$  versus 2.5 $\Omega$  typical, the immediate effect on output voltage is minimal. However, when  $\Phi_1$  propagates through the inverter string, the falling edge of  $\Phi_2$  causes IC<sub>2</sub> to transition from V\_LOW to V\_HIGH. The presence of a low-impedance pullup, R<sub>1</sub>, provides drive for the signal transition, and the closing of IC<sub>2</sub> quickly follows.

The input signal is 5V logic, and the output swings from 1V to 2V (**Figure 2**).

You can set V\_LOW and V\_HIGH to any level within the supply range for IC<sub>1</sub> and IC<sub>2</sub>. The circuit's quiescent current is essentially zero, with brief peaks only during the output transitions. Rise and fall times at the output are approximately 4 nsec, and the output impedance is  $2.5\Omega$ .

Is this the best Design Idea in this issue? Vote at www.ednmag.com/edn mag/vote.asp.

#### Low-battery indicator has high efficiency

Joe Neubauer, Maxim Integrated Products, Sunnyvale, CA

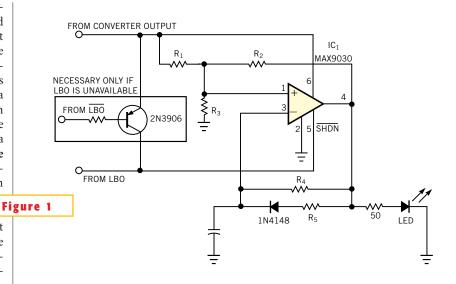

**T** HE USUAL METHOD for implementing the low-battery warning featured in most battery-operated equipment is to illuminate an LED. However, the LED exacerbates the low-battery condition. You can greatly reduce the LED's power consumption by operating it at a low frequency and a low duty cycle. An existing LBO (low-battery output) like that found in dc/dc converters offers a convenient way to light the LED (**Figure** 1). IC<sub>1</sub> is a small, inexpensive comparator with shutdown capability, housed in a six-pin SC70 package. It remains

in shutdown condition while the battery is at normal operating levels but asserts LBO when the battery voltage falls below a preset threshold. Activehigh LBO is usable as shown, but an active-low warning, LBO, requires the optional circuitry shown. IC1 turns on, causing the LED to flash according to the following analysis: First, you want to keep the duty cycle low:  $DC = t_{ON} / (t_{ON} + t_{OFF})$ . You derive the on-time from the equation for time-varying voltage across a charging capacitor:  $V(t) = V(1 - e^{-t/RC})$ , so  $\rm t_{_{ON}}\!=\!-R_{_{5}}Cln(_{_{TRIPHI}}1\!-\!V_{_{TRIPHI}}/V_{_{OUT}}).$  You then derive the off-time from the equation for time-varying voltage across a discharging capacitor:  $V(t) = Ve^{-t/RC}$ , so  $t_{OFF} = -R_4 Cln(V_{TRIPLO}/V_{OUT})$ . Use Kir-

Operating the low-battery LED at low duty cycle saves power and extends battery life.

choff's current laws to find the comparator's high and low trip levels:  $V_{\text{TRIPHI}} = V_{\text{OUT}} [R_3(R_1 + R_2)] / [R_3(R_1 + R_2) + R_1R_2]$ , and  $V_{\text{TRIPLO}} = V_{\text{OUT}} [R_3R_2] / [R_3(R_1 + R_2) + R_1R_2]$ . Assuming a 2.5% duty cycle and assuming that the LBO trips the comparator on when the battery voltage equals 3V, the resulting trip levels are 1V for low and 2V for high. The standard component values corresponding to this performance are:  $C_1 = 0.1 \mu F$ ,  $R_1 = R_2 = R_3 = 1 M\Omega$ ,  $R_4 = 3.6 M\Omega$ , and  $R_5 = 91 k\Omega$ .

Is this the best Design Idea in this issue? Vote at www.ednmag.com/edn mag/vote.asp.

#### LCD-bias supply provides precise tracking

David Kim, Linear Technology Corp, Milpitas, CA

MALL MONOCHROME LCD systems often require split (dual)-bias supplies with precise voltage tracking to prevent plating of the LCD. The circuit in Figure 1 provides ±18 to ±20V adjustable LCD bias voltages with 1% tracking accuracy. The circuit operates from a single 4.2 to 2.5V Li-ion cell for portable monochrome LCD applications. The circuit comprises two blocks: a negativebias supply using the LT1611 inverting switching regulator and a positive-bias supply using the LT1636 rail-to-rail op amp. The LT1611 converts the Li-ion battery input voltage to a negative output voltage. The combination of 1.4-MHz

switching frequency and a 36V internal switch results in small, low-profile circuit. LCD bias requires high voltage at low current. A charge pump consisting of  $C_2$ ,  $C_4$ ,  $D_2$ , and  $D_3$  generates the negative output voltage. Some benefits of this circuit topology include zero output power during shutdown and low output ripple.

The LT1636 rail-to-rail op amp generates the positive LCD-bias output. The large capacitive-load capability, low quiescent current, and high-impedance input stage make the LT1636 suitable in this application. The LT1636 inverts the LT-1611's output to provide the positive LCD-bias voltage. To meet the 1% tracking requirement, you should use a precision-resistor network, such as the 664 series from BI Technologies (www.bitechnologies.com), for R<sub>1</sub> and R<sub>3</sub>. The unique input stage of the LT1636 allows you to generate the V<sub>CC</sub> of the inverting op amp from the rectified switching waveform (using D<sub>1</sub> and C<sub>1</sub>) of the LT1611 switching regulator. You adjust both LCD-bias supplies by varying the 2-k $\Omega$  potentiometer at the feedback node of the LT1611 regulator.

Is this the best Design Idea in this issue? Vote at www.ednmag.com/edn mag/vote.asp.

This LCD-bias supply provides better than 1% tracking of the positive and negative outputs.

#### Rolling-code generator uses flash µC

Wallace Ly, National Semiconductor Corp, Santa Clara, CA

ANY SECURITY-ALARM SYSTEMS require the use of a random number. A computer program uses this random number to create a sequence of ran-

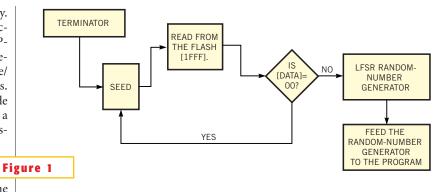

dom numbers to prevent unwanted visitors from gaining entry into a protected facility. You can use a "rolling-code generator" to produce random numbers. To implement such a generator, you would typically need a microcontroller with external memory. Instead, you can use National Semiconductor's COP8SBR flash

μC with "virtual-EEPROM" technology. This technology allows you to use a section of flash memory as if it were EEP-ROM. Because this µC is a true-flash device, the maximum number of erase/ write cycles is typically 100,000 cycles. The flow chart in Figure 1 and the C code in Listing 1 show the adaptation of a textbook LFSR (linear-finite shift register) to the COP8 flash µC.

An initial "seed" first drives the input. The seed then traverses

several exclusive-OR stages. The routine then saves the result to a virtual-EE-PROM location. This approach allows an embedded-system designer to easily create a highly secure system without incurring the cost of an external nonvolatile memory, such as a dedicated serial EEPROM. You can download Listing 1 from EDN's Web site, www.edn-

mag.com. Click on "Search Databases," then enter the Software Center to download the file for Design Idea #2704. You can find additional information about the COP8SBR and its virtual-E<sup>2</sup> feature at www.national.com/cop8.

Is this the best Design Idea in this issue? Vote at www.ednmag.com/edn mag/vote.asp.

// Bit shift left

#### LISTING 1–SOURCE CODE FOR A VIRTUAL-EEPROM BASED RANDOM-NUMBER GENERATOR

```

temp1=temp1>>1;

temp2=temp2>>1;

#include <8cbr.h>

#include <flash_op.h>

if (flag)

temp2.7=1;

/// Description: The following is a random number generator,

// its implementation is the use of a 16 bit

// LFSR, by XORing the correct bits we arrive

// at a pseudo random number

// Use the Carry Bit

temp1.7=carry.0;

//

// Implementation: The pseudo number is created by using the

// feedback equation (for a 16 bit word)

// bit16=bit5 XOR bit4 XOR bit3 XOR bit0

seed_upper=temp1;

seed_lower=temp2;

page_erase(0x1FFF);

// Erase the location

cwritebf(0x1FFF,seed_upper);

cwritebf(0x2000,seed_lower);

// Save the upper byte

// Save the lower byte

void random()(

} // end of the random routine

unsigned int seed_upper; // The seed variables

unsigned int seed_lower;

// Seed the random number generator

// Choose any random numbers for the MSB and

// LSB of the initial random numbers

void main() {

unsigned int i; // A counter variable

unsigned int random_arr[2]; // A random number array

readbf(0x1FFF); // Do a read at the high location seed_upper=ISPRD;

// Set the clock timer

PGMTIM=0x7B;

readbf(0x2000); // Do a read at the low location

seed lower=ISPRD;

// copy it back to the random numbers

readbf(0x1FFF); // Read the result

random_arr[0]=ISPRD; // From the ISPRD register

if (!seed_upper && !seed lower){

// If it is zero then continue

readbf(0x2000);

else {

random_arr[1]=ISPRD;

// Both the Upper and Lower

// Seed

while (1){

seed_upper=10; // Otherwise give it a seed

seed_lower=20;

}

page_erase(0x1FFF);

// Page Erase

// Some Xoring Bits

bits temp1;

bits temp2;

cwritebf(0x1FFF,random_arr[0]); // Write the byte back

cwritebf(0x2000,random_arr[1]); // Write the byte back

char flag;

bits carry;

// Get a number ramdomly generated through 100 iterations

for (i=0;i<100;i++)

// Call the random number

// generator a hundred times

temp1=(bits)seed_upper;

temp2=(bits)seed_lower;

// Assign the upper & lower

random();

carry.0=temp2.5^temp2.4;

carry.0=carry.0^temp2.3;

carry.0=carry.0^temp2.0;

// Now do the Xoring

// Application code goes over here

if (temp2.0)

flag=1;

)

else flag=0;

} // end of main

```

## SEPIC generates 5V at 100 mA

Dongyan Zhou, Linear Technology Corp, Milpitas, CA

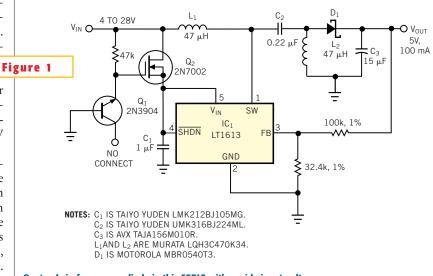

**S** OME APPLICATIONS REQUIRE an input voltage higher than the breakdown voltage of the IC supply pin. In boost converters and SEPICs (singleended primary-inductance converters), you can separate the  $V_{IN}$ pin of the IC from the input inductor and use a simple zener regulator to generate the supply voltage for the IC. Figure 1 shows a SEPIC that takes a 4 to 28V input and generates 5V at 100 mA.

In this application,  $Q_1$  and  $Q_2$  generate the supply voltage for IC<sub>1</sub> because the supply voltage exceeds IC<sub>1</sub>'s maximum input voltage. The circuit uses  $Q_1$  in place of a zener diode to save cost. The emitter-to-base breakdown voltage gives a stable 6V reference. The follower,  $Q_2$ , provides the supply voltage for the IC. This circuit demonstrates an inexpensive way to extend the input range of the IC.

This SEPIC can step up or step down the input voltage. Because the flying capacitor,  $C_2$ , breaks the input-to-output dc path, the output disconnects from the input when you shut down the device, in-

${\bf Q}_{_1}$  stands in for a zener diode in this SEPIC with a wide input-voltage range.

hibiting any possible load current in shutdown mode, which is important for portable applications and which prevents the input voltage from appearing at the output. Is this the best Design Idea in this issue? Vote at www.ednmag.com/edn mag/vote.asp.

### Look-up table helps bit flipping

Brad Bierschenk, High End Systems, Austin, TX

N CERTAIN INSTANCES in embedded software, a programmer needs to flip the order of the bits in a byte so that  $B_7$  to  $B_0$  become  $B_0$  to  $B_7$ . Bit flipping is useful, for example, when a synchronous serial port does not allow programmatic selection of bit order, such as MSB first or LSB first, for its shift register. You need a software method to translate data if the processor sends data to a receiving device that expects a certain bit order, but the serial port can provide only the other bit order.

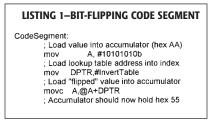

One solution is to provide a look-up table in ROM in which the value of each byte in the table is its offset into the table but with a reversed bit order. In other words, the first byte is offset 0

(0000000b), the second byte is offset 1 (10000000b), the third byte is offset 2 (01000000b), and so on. The program needs only to load the value to be translated into a register that you can use as an offset, index the look-up table, and load the corresponding value from the index+offset location (**Listing 1**). Using the Philips  $8 \times C51$  architecture as an ex-

ample, you can use the 16-bit DPTR (data pointer) plus an 8-bit offset in accumulator (A) to load the accumulator with a byte value.

This approach is dynamically more efficient than rotating a byte location through carry bits, but it is not the most statically efficient approach because the look-up table requires 256 bytes of ROM. You can download the inversion table from *EDN*'s Web site, www.ednmag.com. Click on "Search Databases" and then enter the Software Center to download the file for Design Idea #2621.

Is this the best Design Idea in this issue? Vote at www.ednmag.com/edn mag/vote.asp.