# Configuring and Applying the MC74HC4046A Phase-Locked Loop

A versatile device for 0.1 to 16MHz frequency synchronization

Prepared by Cleon Petty Gary Tharalson Marten Smith Motorola Applications Engineering

2/98

## Configuring and Applying the MC74HC4046A Phase–Locked Loop A versatile device for 0.1 to 16MHz frequency synchronization

The MC74HC4046A (hereafter designated HC4046A) phase–locked loop contains three phase comparators, a voltage–controlled oscillator (VCO) and an output amplifier. The user of this document should have a copy of the HC4046A data sheet in Motorola Data Book DL129 available for details of device operation and operating specifications. The user should also be aware that the following information is useful for approximating a design **but**, because of process, layout and other variables, there can be substantial deviation between theory and actual results. Therefore, **it is highly recommended that prototypes be built and checked before committing a design to production**.

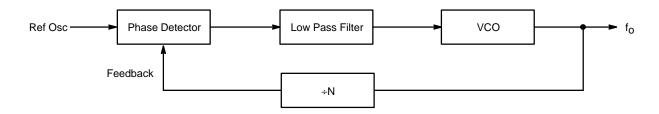

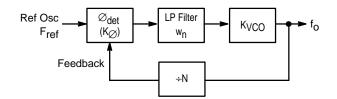

Typical applications for the HC4046A usually involve a configuration such as shown in Figure 1.

Figure 1. Typical Phase–Locked Loop

### **VCO/OUTPUT FREQUENCY**

The output frequency,  $F_0,$  is calculated as a function of the Ref Osc input and the  $\div N$  feedback counter:

$$F_0 = \text{Ref Osc} * N$$

(1)

The ability of the loop to emulate the above formula makes it ideal for multiplying an input frequency by any number up to the maximum of the VCO. The HC4046A VCO frequency is controlled by the equation:

VCO freq =

$$f(I * C)$$

(2)

where I is controlled by the external resistors  ${\sf R}_1$  and  ${\sf R}_2$  and C by external capacitor  ${\sf C}_{ext}$  .

Frequency of oscillation is calculated by starting with the familiar equation:

$$I = c \frac{dV}{dt}$$

(3)

and reworking it to obtain a formula that incorporates all the detail to fit the HC4046A. First, the charge time of the device for half–cycle time is obtained as follows:

dt = dV

$$\frac{C}{I}$$

and  $F_0 = \frac{1}{2dt}$

or,  $F_0 = \frac{\frac{1}{2CdV}}{I} = \frac{I}{2CdV}$  (4)

where I and dV must be obtained for the HC4046A.

There are two components that comprise the I charge for the HC4046A VCO, I<sub>1</sub> and I<sub>2</sub>. I<sub>1</sub> is the current that sets the frequency associated with the VCO input and is a function of R<sub>1</sub>, VCO<sub>in</sub>, and an internal current mirror that is ratioed at 120/5  $\approx$  24, resulting in the equation:

$$I_1 = \frac{VCO_{in}}{R_1} \left(\frac{120}{5}\right) \tag{5}$$

$I_2$  is set by  $R_2$  and adds a constant current to limit the  $F_0$  min of the VCO and is a function of  $V_{dd},\,R_2,$  and an internal current mirror of ratio 23/5, resulting in the equation:

$$I_{2} = \left(\frac{2V_{dd}}{3R_{2}}\right) \left(\frac{23}{5}\right)$$

(6)

The dV of Equation (4) is determined by design to be  $\approx 1/3$  V<sub>dd</sub>. Substituting this and I = I<sub>1</sub> + I<sub>2</sub> into Equation (4) results in:

$$F_{O} = \frac{\frac{VCO_{in}}{R_{1}} \left(\frac{120}{5}\right) + \left(\frac{2V_{dd}}{3R_{2}}\right) \left(\frac{23}{5}\right)}{2C_{ext} \frac{V_{dd}}{3}}$$

$$= \frac{\frac{VCO_{in}}{R_{1}} (24) + \left(\frac{2V_{dd}}{3R_{2}}\right) (4.6)}{2C_{ext} \frac{V_{dd}}{3}}$$

$$= \frac{\frac{3VCO_{in}}{R_{1}} (24) + \frac{2V_{dd}}{R_{2}} (4.6)}{2C_{ext} V_{dd}}$$

(7)

It was found by experiment that when the  $C_{ext}$  potential reaches threshold (at  $V_{dd}/3$ ), the inversion of the charging voltage of  $C_{ext}$  is forced below ground due to charge coupling. Therefore, the dV is not just  $V_{dd}/3$  as expected and the charg-

ing time must start at a point below ground which affects t and thus,  $F_0$ . An undershoot voltage must be added to the equation for better accuracy in calculating t and  $F_0$ . This modifies Equation (7) as follows:

$$F_{0} = \frac{\frac{3VCO_{in}}{R_{1}}(24) + \frac{2V_{dd}}{R_{2}}(4.6)}{2C_{ext} (Vdd + 3 * undershoot)}$$

$$= \frac{\frac{3VCO_{in}(I_{constant ratio})}{R_{1}} + \frac{9.2(V_{dd})}{R_{2}}}{2C_{ext} (Vdd + 3 * undershoot)}$$

(8)

Equation (8) now contains all the factors to calculate an  $F_0$  for the HC4046A VCO.

It was determined by experiment that the undershoot of the charging waveform is a function of  $C_{ext}$  and an on-chip parasitic diode that clamps it at a maximum of -0.7V. The size of the  $C_{ext}$  capacitor limits the voltage and was found to be near zero volts for  $C_{stray} \approx 17 pF \le C_{ext} \le 30 pF$ ; the voltage increases at 6 mV/pF for a  $30 pF \le C_{ext} \le 150 pF$  range of  $C_{ext}$ . The on-chip diode then takes over and limits the voltage to -0.7V.

It was also found that the I<sub>constant ratio</sub> is a function of R<sub>1</sub> and increases as R<sub>1</sub> becomes larger. The change is attributed to saturation of the current mirror at lower value resistances, and to voltage divider problems at higher value resistances combined with the resistance of the small FET in the current mirror. Experimental data shows that I<sub>constant</sub> ratio follows Table 1 somewhat. The ratio goes to 25 somewhere between 9.1K $\Omega$  and 51K $\Omega$ , and for those limits, 25 should give reasonable results. In addition, these numbers seem to hold for a range of V<sub>dd</sub> of 3.0V  $\leq$  V<sub>dd</sub>  $\leq$  6V.

| R <sub>1</sub> (ΚΩ) | Iconstant ratio |  |

|---------------------|-----------------|--|

| 3.0                 | 13.5            |  |

| 5.1                 | 17.5            |  |

| 9.1                 | 21.5            |  |

| 12                  | 23.0            |  |

| 15                  | 24.0            |  |

| 30                  | 26.5            |  |

| 40                  | 27.0            |  |

| 51                  | 28.5            |  |

| 110                 | 29.0            |  |

| 300                 | 31.0            |  |

The VCO calculation [Equation (8)] becomes a bit more accurate by adjusting the VCO<sub>in</sub> and I<sub>constant ratio</sub>. For example, with R<sub>1</sub> = 300K, R<sub>2</sub> =  $\infty$ , C<sub>ext</sub> = 0.1 $\mu$ F, VCO<sub>in</sub> = 1.0V, V<sub>dd</sub> = 4.5V, and I<sub>constant ratio</sub> = 31, Equation (8) yields:

$$F_{O} = \frac{\frac{(3)(1)(31)}{300K}}{2(0.1 * 10^{-6})(4.5 + 2.1)}$$

$$= 235Hz$$

For comparison, from Chart 14D in the HC4046A data sheet, the  $F_0$  based on measurements is approximately 270 Hz. Thus, the calculated and measured values are not too far apart taking into consideration such variables as process variation, temperature, and breadboard inaccuracies. The C<sub>stray</sub> of a PCB layout will affect results if the  $C_{ext}$  is not  $\gg C_{stray}$ . So for  $C_{ext} \leq$  1000pF, adding  $C_{stray}$  to the  $C_{ext}$  fixed capacitance will result in better accuracy.

The gain of a VCO is calculated by knowing  $f_{max}$  at VCO\_{in} max and  $f_{min}$  at VCO\_{in}min and calculating the following equation:

VCO gain =

$$\frac{f_{max} - f_{min}}{VCO_{in} max - VCO_{in} min}$$

(9)

$$= \Delta freq/volt$$

The gain of the VCO is needed to calculate a suitable loop filter for a PLL system.

$F_{0}$  is determined by VCO<sub>in</sub> and is clamped as a function of a % of V<sub>dd</sub>. The clamp voltage generally follows the slope of 4%/V for V<sub>dd</sub> changes from  $3.5V \le V_{dd} \le 6V$ , starting at 56% at V<sub>dd</sub> = 3.5V and going to 66% at V<sub>dd</sub> = 6V. Knowing this limit point allows picking a VCO<sub>in</sub> max point a few hundred mV below it and keeps  $F_{0}$  in the linear range of operation. It also best to pick a VCO<sub>in</sub> min point at a level of a few hundred mV above 0V for the same reason given above.

As an example, for a C<sub>ext</sub> =1100pF, R<sub>1</sub> = 9.1K, R<sub>2</sub> =  $\infty$ , V<sub>dd</sub> =5.0V, and VCO<sub>in</sub> min = 0.25V, VCO<sub>in</sub> max can be determined and a gain calculated as follows. VCO<sub>in</sub> limit = (4%/V)(1.5V) + 56% = (62%)(V<sub>dd</sub>) = 3.1V. So, for sake of linearity, choose VCO<sub>in</sub> = 2.5V. Using Equation (8), VCO<sub>in</sub> min and VCO<sub>in</sub> max can be used to calculate F<sub>o</sub> min and F<sub>o</sub> max as follows:

$$F_{0} \text{ min} = \frac{\frac{(3)(0.25)(21.5)}{9.1K}}{2(1100 * 10^{-12})(5 + 2.1)} = 113.4 \text{KHz}$$

$$F_{0} max = \frac{\frac{(3)(2.5)(21.5)}{9.1K}}{2(1100 * 10^{-12})(5 + 2.1)} = 1.3 MHz$$

Then, using Equation (9), the VCO gain is:

VCO gain =

$$\frac{1.3 \times 106 - 0.11 \times 106}{2.5 - 0.25} = 528.9 \text{KHz/V}$$

This gain factor will be known as  $K_{\text{VCO}}$  in the loop filter equations.

$R_2$  is used in applications where a minimum output frequency is desired when VCO<sub>in</sub> is 0V. It is calculated at VCO<sub>in</sub> = 0V causing Equation (8) to become:

$$F_0 = \frac{9.2 (V_{dd})}{2C (R_2) (V_{dd} + 3 * undershoot)}$$

The additional I<sub>2</sub> current is a constant that adds to total charge current for C<sub>ext</sub> and increases the VCO<sub>in</sub> versus F<sub>0</sub> curve by a theoretical constant amount. In reality, the amount of increase actually decreases at a slight rate as VCO<sub>in</sub> increases. The decrease is slight and the use of Equation (8) will give adequate accuracy for most applications.

The  $F_{max}$  of the HC4046A VCO was determined to be about 16MHz. Beyond 16MHz, the output logic swing tends to reduce and is therefore somewhat useless for driving a CMOS input. The VCO will operate at  $\approx$  28MHz but the output has a VOL $\approx$  2.0V and a VOH $\approx$  4.5V at Vdd = 5.0V.

The following table was generated to make calculation of R<sub>1</sub> and C<sub>ext</sub> a function of F<sub>0</sub> with V<sub>dd</sub> = 5V, VCO<sub>in</sub> = 1V, and room temperature. Use of the table allows a rough estimate of (R<sub>1</sub>)(C<sub>ext</sub>) for a given F<sub>0</sub>. The final values can be adjusted by use of Equation (8), Table 1 for I<sub>constant ratio</sub>, rules for undershoot voltage, V<sub>dd</sub> variations, and VCO<sub>in</sub> variations. The example below shows a typical calculation.

Table 2. (R<sub>1</sub>)(C<sub>ext</sub>) versus F<sub>0</sub>

| R <sub>1</sub> (Ω)          | C <sub>ext</sub> (pF)                                                                                             | (R <sub>1</sub> )(C <sub>ext</sub> )                              |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| $3.0K \le R_1 \le 9.0K$     | $\begin{array}{l} 0 \leq C_{ext} \leq 30 \\ 30 \leq C_{ext} \leq 150 \\ 150 \leq C_{ext} \leq \infty \end{array}$ | 5.40/F <sub>0</sub><br>4.15/F <sub>0</sub><br>3.80/F <sub>0</sub> |

| 9.1K ≤ R <sub>1</sub> ≤ 50K | $\begin{array}{l} 0 \leq C_{ext} \leq 30 \\ 30 \leq C_{ext} \leq 150 \\ 150 \leq C_{ext} \leq \infty \end{array}$ | 7.50/F <sub>0</sub><br>5.77/F <sub>0</sub><br>5.28/F <sub>0</sub> |

| 50K ≤ R <sub>1</sub> ≤ 900K | $\begin{array}{l} 0 \leq C_{ext} \leq 30 \\ 30 \leq C_{ext} \leq 150 \\ 150 \leq C_{ext} \leq \infty \end{array}$ | 9.00/F <sub>0</sub><br>6.92/F <sub>0</sub><br>6.34/F <sub>0</sub> |

Assume a desired value of F<sub>0</sub> of 1MHz. From Table 2, choose an R<sub>1</sub> range of 9.1K  $\leq$  R<sub>1</sub>  $\leq$  50K and a C<sub>ext</sub> range of > 150pF; this condition leads to (R<sub>1</sub>)(C<sub>ext</sub>) = 5.28/F<sub>0</sub>. Thus,

(R<sub>1</sub>) (C<sub>ext</sub>) =

$$\frac{5.28}{1*10^6}$$

= 5.28 \* 10<sup>-6</sup>

Now choose a Cext of 200pF. Then, from above result,

$$R_1 = \frac{5.28 * 10^{-6}}{200 * 10^{-12}} = 26K$$

This appears reasonable and there are standard values for  $C_{ext} = 200pF$  and  $R_1 = 27K$ . Using these values, Equation (8) can be adjusted according to the desired  $F_0$  min,  $F_0$  max, and  $F_0$  center.

#### LOW PASS FILTER DESIGN

The design of low pass filters is well known and the intent here is to simply show some typical examples. Reference should be made to the HC4046A Data Sheet and to Motorola Application Note AN535/D — "Phase–Locked Loop Fundamentals" (available through Motorola Literature Distribution).

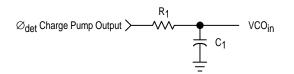

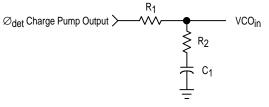

Some simple types of low pass filters are shown in Figure 2 and Figure 3.

Figure 3. Simple Low Pass Filter B

The equations for calculating loop natural frequency  $(w_{\mbox{n}})$  and damping factor (d) are as follows:

For Filter A (Figure 2):

$$w_{n} = \sqrt{\frac{K_{\emptyset}K_{VCO}}{NC_{1}R_{1}}}$$

$$= 0.5w_{n}$$

**K**øKVCO

where  $K_{\not O}$  = phase detector gain,  $K_{VCO}$  = VCO gain, and N = divide counter.

For Filter B (Figure 3):

$$w_{n} = \sqrt{\frac{K_{\emptyset}K_{VCO}}{NC_{1}(R_{1} + R_{2})}}$$

$$d = 0.5w_{n}(R_{2}C_{1} + \frac{N}{K_{\emptyset}K_{VCO}}) \qquad (10)$$

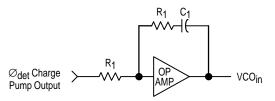

Figure 4 shows an active filter using an op amp from Application Note AN535/D.

#### Figure 4. Op Amp Filter

For Figure 4, the equations become:

$$w_{\rm n} = \sqrt{\frac{K_{\emptyset}K_{\rm VCO}}{NC_1R_1}} \tag{11}$$

$$d = \frac{K_{\emptyset}K_{VCO}R_2}{2w_nNR_1}$$

(12)

$$=\frac{w_nC_1R_2}{2}$$

, where Op Amp gain is large

From the above equations, it is possible to design a suitable filter to meet the needs of many PLL applications. The inclusion of  $R_2$  in the equations for Figure 3 and Figure 4 permits the capability to change  $w_n$  and d separately while Figure 2

equations do not. Normally, a design is easier if  $w_n$  and d can be chosen independently. Both factors affect the loop acquisition time and stability. A good starting value for d is 0.707 and  $F_{ref}/10$  for  $w_n$ .

Manipulation of the equations allows calculation of  $R_1$ ,  $R_2$ , and  $C_1$  from the other measured, calculated, or picked parameters. For example,

$$R_1 + R_2 = \frac{K_{\emptyset}K_{VCO}}{NC_1 w_n^2}$$

(13)

$$R_{2} = \frac{2d}{C_{1}w_{n}} - \frac{N}{C_{1}(K_{\emptyset}K_{VCO})}$$

(14)

$$C_1 = \frac{K_{\emptyset}K_{VCO}}{Nw_n^2(R_1 + R_2)}, \text{ or alternatively,}$$

$$c_1 = \frac{2d}{R_2 w_n} - \frac{N}{R_2 (K_{\emptyset} K_{VCO})}$$

Usually,  $C_1$ ,  $w_n$ , and d are picked and the remaining parameters calculated.

#### **DESIGN EXAMPLE**

The goal is to design a phase–locked loop that has an  $F_{ref}$  of 100KHz, an output  $F_0$  of 1MHz center frequency, and the ability to move from 200KHz to 2MHz in 100KHz steps.

Figure 5. Parametized PLL

To determine N, use equation (1) for  $F_0$  min = 200KHz, and  $F_0$  max = 2MHz resulting in the following:

N min = 200/100 = 2, and

N max = 2000/100 = 20

The results so far indicate the following starting parameters:

A. A VCO with a 10:1 range is required B.  $w_n = F_{ref}/10 = 10$ KHz C. d = 0.707 D.  $R_2 = \infty$ E.  $V_{dd} = 5.0$ V The  $F_0$  center frequency  $\approx$

$$\frac{F_{max} + F_{min}}{2} = \frac{2.0 + 0.2}{2} = 1.1 \text{MHz}$$

Recalling that the clamp voltage % at V<sub>dd</sub> = 5V is about 62, then F<sub>max</sub> VCO<sub>in</sub> limit = (0.62)(5) = 3.1V, but as described earlier, this needs to be reduced by a factor to bring it into linearity ( $\approx$  350mV) so the final F<sub>max</sub> VCO<sub>in</sub> limit = 2.75V.

For the  $F_{min}$  VCO\_{in} limit pick 0.25V. This results in a center frequency VCO\_{in} of:

Center freq VCO<sub>in</sub> =

$$\frac{2.75 - 0.25}{2}$$

= 1.25V

From Table 2, for picked values of  $9.1K \le R_1 \le 50K$  and  $30 \le C_{ext} \le 150$ , obtain an estimate for  $(R_1)(C_{ext})$  of  $5.77/F_0$ . Thus, at the F<sub>0</sub> center frequency,

$$(R_1)(C_{\text{ext}}) = \frac{5.77}{1.1 \cdot 10^6} = 5.245 \cdot 10^{-6}$$

Now, a reasonable starting point is established for setting the values of the loop filter and the VCO range. Choosing  $R_1 = 9.1K$ ,  $C_{ext}$  becomes

$$C_{ext} = \frac{5.245 * 10^{-6}}{9.1K} = 576 pF WHOOPS!$$

This value, 576pF, is outside of the original picked range for  $C_{ext}$ ; therefore, we need to go back and pick a larger value of  $R_1$ , e.g., 42K should be sufficient. Then  $C_{ext}$  becomes

$$C_{ext} = \frac{5.245 * 10^{-6}}{42K} = 125 pF$$

and now both R1 and Cext are within selected ranges.

Now calculate F<sub>max</sub> and F<sub>min</sub> using Equation (8) with R<sub>1</sub> =  $42k\Omega$ , R<sub>2</sub>= $\infty$ , V<sub>dd</sub>=5.0V, I<sub>constant ratio</sub>=27 (from Table 1. and R<sub>1</sub> =  $42k\Omega$ ), V<sub>undershoot</sub> = 0.57V (calculated from 6pF/mV (125pF–30pF)=0.57V), VCO<sub>in</sub> min=0.25V, and VCO<sub>in</sub> max = 2.75V:

$$F_{0} \min = \frac{\frac{(3)(0.25)(27)}{42K} + \frac{(9.2)(5.0)}{\infty}}{(2)(125 * 10^{-12}f) [5.0V + 3(0.57V)]}$$

$$= \frac{20.25}{70.455 * 10^{-6}} = 287.4 \text{KHz}$$

$$F_{0} \max \frac{\frac{(3)(2.75)(27)}{42K} + \frac{(9.2)(5.0)}{\infty}}{(2)(125 * 10^{-12}f) [5.0V + 3(0.57V)]}$$

$$= \frac{222.75}{70.455 * 10^{-6}} = 3.16$$

MHz

$F_{max}$  is > the required 2.0MHz, but the  $F_{min}$  is not low enough for required application. It is necessary to adjust either  $C_{ext}$  or  $R_1$  to achieve required specification of 0.2 to 2.0MHz  $F_0$ . Since  $R_1 = 42k\Omega$  is a standard resistor value, try adjusting  $C_{ext}$  to a higher value, such as 175pF. Because  $C_{ext}$  is now > 150pF, the  $V_{undershoot}$  must be adjusted to 0.7V, as per earlier explanation:

So,

$$F_{0} \min = \frac{\frac{(3)(0.25)(27)}{42K} + \frac{(9.2)(5.0)}{\infty}}{(2)(175 * 10^{-12} \text{f}) [5.0V + 3(0.7V)]}$$

$$= \frac{20.25}{104.37 * 10^{-6}} = 194.02 \text{KHz}$$

and

$$F_{0} \max \frac{\frac{(3)(2.75)(27)}{42K} + \frac{(9.2)}{\infty}}{(2)(175 * 10^{-12} f) [5.0V + 3(0.7V)]}$$

$$=\frac{222.75}{104.37*10^{-6}}=2.13$$

MHz

These values are adequate for the specified application.

The next item to determine is the VCO gain factor,  $K_{VCO}$ , using Equation (9):

$$K_{VCO} = \frac{f_{max} - f_{min}}{VCO_{in} max - VCO_{in} min}$$

$$K_{VCO} = \frac{2.13 * 10^{6} - 0.194 * 10^{6}}{2.75V - 0.25V} = 774.4KHz/V$$

or in radians

-

$$= (2\pi) (774.4 * 10^3) = 4.86 * 10^6 \text{Rad/sec/V}$$

The final values used for the desired frequency range are R<sub>1</sub> = 42k $\Omega$ , C<sub>ext</sub> = 175pF, R<sub>2</sub> =  $\infty$ , VCO<sub>in</sub> max = 2.75V, and VCO<sub>in</sub> min = 0.25V.

The next step is to determine the loop filter. Choosing a filter like the one in Figure 3, calculate the component as follows:

$$\begin{split} \mathsf{K}_{\varnothing} &= \frac{\mathsf{V}_{dd}}{4\pi} = \frac{5.0}{4\pi} = \ 0.4 \mathsf{V}/\mathsf{rad} \\ \mathsf{w}_{\mathsf{n}} &= \frac{100\mathsf{K}\mathsf{Hz}}{10} = \ 10\mathsf{K}\mathsf{Hz} * 2\pi = \ 62.83 * 10^3\mathsf{rad}/\mathsf{sec} \\ \mathsf{d} &= 0.707 \text{ (for starters), and} \end{split}$$

where

$K_{\emptyset}$  = phase detector gain  $V_{dd}$  = output swing

Choose  $C_1$  to be  $0.01\mu$ F, N = 10 for approximate mid-range  $F_0$ , and calculate  $R_1$  and  $R_2$  using Equations (13) and (14):

$$R_{1} + R_{2} = \frac{K_{\emptyset}K_{VCO}}{NC_{1}w_{n}^{2}} = \frac{(0.4)(4.86 * 10^{6})}{(10)(0.01 * 10^{-6})(62.83 * 10^{3})^{2}}$$

$$= \frac{1.944 * 10^{6}}{394.76} = 4924.5\Omega$$

$$R_{2} = \frac{2d}{C_{1}w_{n}} - \frac{N}{C_{1}(K_{\emptyset}K_{VCO})}$$

$$= \frac{(2)(0.707)}{(0.01 * 10^{-6})(62830)} - \frac{10}{(0.01 * 10^{-6})(0.4)(4.86 * 10^{6})}$$

$$= 2250.52 - 514.4 = 1736\Omega$$

Then,  $R_1 = 4924.5 - 1736 = 3188.5\Omega$ .

Since N is changeable, it is a good idea to check min and max on w<sub>n</sub> and d. For more information on why, see Motorola Application Note AN535/D or the MC4044 Data Sheet in the MECL Data Book DL122/D. The following examples show sample calculations for N = 2 and 20.

For N = 20, use Equation (10) to calculate  $w_n$  and d:

$$w_{n} \min = \sqrt{\frac{K_{\emptyset}K_{VCO}}{NC_{1}(R_{1} + R_{2})}}$$

$$= \sqrt{\frac{(0.4)(4.86 * 10^{6})}{(20)(0.01 * 10^{-6})(3188.5 + 1736)}}$$

$$= 44.43 * 10^{3} \text{rad/sec, or}$$

$= \frac{44.43 * 10^3 \text{rad/sec}}{2\pi} \approx 7 \text{KHz}$

and

$$d_{min} = (0.5)(w_n) \left[ R_2 C_1 + \frac{N}{K_{\emptyset} K_{VCO}} \right]$$

$$= (0.5)(44.43 * 10^{3}) * \left[ (1736)(0.01 * 10^{-6}) + \frac{20}{(0.4)(4.86 * 10^{6})} \right]$$

= 0.6144

For N = 2:

$$w_{\text{n}} \max = \sqrt{\frac{(0.4)(4.86 * 106)}{(2)(0.01 * 10^{-6})(3188.5 + 1736)}}$$

$$= 140.49 * 10^{3} \text{rad/sec, or}$$

$$= \frac{140.49 * 10^{3} \text{rad/sec}}{2} = 22.36 \text{KHz}$$

2π

and

$$d_{\text{max}} = (0.5)(140.49 * 10^3) * \left[ (1736)(0.01 * 10^{-6}) + \frac{2}{(0.4)(4.86 * 10^6)} \right]$$

= 1.292

This shows the effect of changing n on loop performance and for this application is adequate.

If the components are not what is desired, choosing a different  $w_n$  and/or d allows them to be modified.

Alternatively, picking different C,  $R_1$  or  $R_2$  and recalculating the other parameters can be done. If the filter does not provide adequate performance, making  $w_n$  smaller or d larger may improve stability.

Note: Application Note AN535/D can also be found in BR1334/D, Motorola's High Performance Frequency Control Products book, also available through the literature distibution center.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights or the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and **(A)** are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1–303–675–2140 or 1–800–441–2447

Customer Focus Center: 1-800-521-6274

Mfax™: RMFAX0@email.sps.mot.com

– TOUCHTONE 1–602–244–6609

Motorola Fax Back System

– US & Canada ONLY 1–800–774–1848

– http://sps.motorola.com/mfax/

HOME PAGE: http://motorola.com/sps/

Mfax is a trademark of Motorola, Inc.

JAPAN: Nippon Motorola Ltd.: SPD, Strategic Planning Office, 141, 4–32–1 Nishi–Gotanda, Shagawa–ku, Tokyo, Japan. 03–5487–8488

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298